Turinys

Įvadas.

Bendros sąvokos ir apibrėzimai.

Skaičiavimo sistemos ir veiksmai su skaičiais

Dvejetainiai skaičiai ir veiksmai su jais

Aritmetiniai veiksmai su dvejetainiais skaičiais

Sesioliktainiai skaičiai ir veiksmai su jais

Dvejetainis desimtainis kodas

Skaitmeniniai signalai ir elementarūs loginiai elementai.

Baziniai loginiai elementai

Mikroprocesorinių sistemų operaciniai įtaisai.

MIKROPROCESORIAI

Truputi istorijos

Mikroprocesorių parametrai

Vidinė mikroprocesoriaus sandara

Aritmetinis - loginis įtaisas

Mikroprocesoriaus registrai

Valdymo schemos

Vidinės mikroprocesoriaus magistralės

Adresavimo būdai

Tiesioginis ir segmentinis adresavimas

Mikroprocesoriaus komandų sandara

Mikroprocesoriaus veikimo sparta

Vidutinė komandos vykdymo trukmė.

Mikroprocesoriaus veikimo spartinimo būdai

Apie mikroprocesorių konstrukcijas

Adresų ir duomenų magistralių sugretinimas.

Mikroprocesoriaus valdymo signalai.

MIKROPROCESORINIŲ ĮTAISŲ ATMINTINĖS

Atmintinių tipai ir parametrai

Atmintinių tipai

Pagrindiniai atmintinių parametrai

Statinių (SRAM) atmintinių mikroschemos

Dinaminės atmintinės

Programuojamosios atmintinės

Informacijos pasikeitimo tarp mP ir atmintinės spartinimo būdai

Spartinančioji atmintis (SA)

Tiesioginio kreipimosi į atmintinę rezimas

ISORINIŲ ĮRENGINIŲ SĄSAJOS

Sąsaja ir sąsajos valdiklis

Proceso informacijai įvesti ir isvesti organizavimo principai

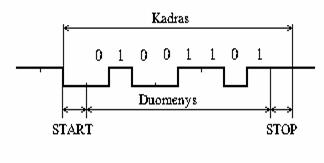

Nuosekliojo rysio sąsaja

RS232 standartas

Nuosekliojo rysio programuojamos sąsajos mikroschema 82510

Lygiagrečiojo rysio sąsaja

Bendrosios zinios

Lygiagrečiosios programuojamos sąsajos mikroschema 8255A

ELEKTRONINIAI MIKROPROCESORINIAI ĮTAISAI IR VALDIKLIAI

Mikroprocesoriumi (MP) vadiname programiniu būdu valdomą skaitmeninės informacijos apdorojimo įtaisą, sudarytą is vienos ar kelių didelės integracijos mikroschemų. Mikroprocesorių sudaro du įtaisai: operacinis įtaisas, atliekantis operacijas su operandais, ir valdantysis įtaisas, kuris suformuoja valdančiuosius signalus operaciniam įtaisui pagal is atminties nuskaitytą komandos kodą.

Mikroprocesoriniu įtaisu (MĮ) arba mikroprocesorine sistema (MPS) vadinamas elektroninis įtaisas, kuriame yra bent vienas mikroprocesorius. MĮ naudojami pramonėje, medicinoje, buityje ir daugelyje kitų sričių. Pavyzdziui, MĮ yra personalinis kompiuteris, staklių ir mikrobanginės krosnelės valdymo įranga, elektroninis laikrodis ir t.t. Bendru atveju mikroprocesorinį įtaisą (1 pav.) sudaro mikroprocesorius, atmintis (programų ir duomenų) bei periferiniai įvedimo - isvedimo įrenginiai (I/O). MĮ skirtas skaitmeninio informacijos apdorojimo algoritmų programinei realizacijai. Pagrindinis informacijos apdorojimo elementas čia yra mikroprocesorius. Mikroschemų skaičius, sudarantis mikroprocesorinį įtaisą, svyruoja nuo vieno iki keleto desimčių.

1. pav. Mikroprocesorinio įtaiso blokinė schema

Mikroprocesorius apdoroja informaciją. Sistemine magistrale (System Bus) cirkuliuoja duomenys, adresai ir valdymo signalai. Pastoviojoje atmintinėje (ROM - Read Only Memory) saugoma minimali informacija, būtina įtaiso sistemos veikimui valdyti. Joje gali būti programa valdanti viso įtaiso veikimą. Operatyviojoje atmintinėje (RAM - Random Access Memory) saugomi duomenys, tarpiniai skaičiavimų rezultatai ir įtaiso valdymo programos. Programa į atmintinę įrasoma nuosekliai. Per sąsajas (Interface) MĮ bendrauja su kitais įrenginiais, gauna is jų ir jiems siunčia informaciją. MĮ gali būti keli vienodi ar skirtingi mikroprocesoriai, jis gali turėti kelias sąsajas, įvairių tipų bei paskirties magi 18418x2320s strales ir atmintines.

Galimi tokie mikroprocesorinių sistemų funkcinių elementų realizavimo atvejai:

- vieno elemento funkcijas realizuoja keletas IS;

- kiekvieną funkcinį elementą atitinka atskira didelės integracijos schema (DIS), realizuojanti jo funkcijas;

- keli (ribiniu atveju visi) funkciniai elementai realizuoti vienoje DIS.

Jeigu visi MĮ-so funkciniai elementai yra vienoje didelės integracijos schemoje, jis vadinamas vienkristaliu mikrovaldikliu (Microcontroller). Jeigu mikrovaldiklio (MV) savųjų resursų nepakanka, jie isplečiami isorinių įrenginių (atminties ir isorinių sąsajų) sąskaita. Tokiu atveju mikrovaldiklis veikia mikroprocesoriaus rezimu. Mikrovaldiklio struktūros pavyzdys - Texas Instruments MSP430F449 (2 pav.), kuriame integruota dauguma mikroprocesorinėms sistemoms būdingų funkcinių blokų:

aritmetinis loginis įrenginys (CPU);

aparatinis daugiklis (Multiply);

sinchronizacijos blokas (Oscillator);

programų ir duomenų atmintys (ROM ir RAM);

įvedimo - isvedimo prievadai (I/O ports

keitiklis analogas kodas (ADC);

nuoseklaus rysio sąsajos (USART0 ir USART1);

budintis laikmatis (Watchdog

laikma iai (Timer A, Timer B, Basic Timer);

informacijos isvedimo į skystųjų kristalų displėjų kontroleris (LCD controller);

analoginių signalų palyginimo įtaisas (Comparator A

maitinimo įtampos būsenos sekimo įtaisas (Brownout).

Mikrovaldiklio struktūros pavyzdys (Texas Instruments MSP430F449)

Procesorinis elementas gali būti sudarytas is kelių DIS, kurios atlieka procesoriaus valdančiojo bei operacinio įtaiso funkcijas. Tokio procesoriaus skilčių skaičius priklauso nuo sujungtų į bendrą modulį operacinio įtaiso funkcijas atliekančių mikroschemų kiekio, o toks įtaisas vadinamas daugelio kristalų mikroprocesoriumi.

Mikroprocesorinės sistemos architektūra sąvoka apjungia:

- vidinės architektūros tipą (Harvardo - kai mikroprocesorius naudoja atskiras magistrales duomenims ir komandoms įvesti / isvesti, ar Von Neumano - kai duomenų ir komandų skaitymui / rasymui naudojama ta pati magistralė);

rysio su mikroprocesorinės sistemos mazgais metodus ir priemones;

sąsajos skilčių skaičių ir organizavimo principus;

registrų kiekį ir darbo su jais būdus;

duomenų formatą;

komandų sąrasą ir adresavimo metodus;

- pertraukčių aptarnavimo būdus.

rograminiu būdu valdomas skaitmeninės informacijos apdorojimas. Mikroprocesorius operuoja tik dvejetainiais duomenimis, todėl norint issiaiskinti mikroprocesoriaus veikimo principus svarbu perprasti pagrindines skaičiavimo sistemas.

Dvejetainė skaičiavimo sistema - tai skaičiavimo sistema, kurios skaičiai susideda is 1 ir 0, priklausomai nuo pozicijos turinčių skirtinga svorį - pagrindą 2 pakelto laipsniu, lygiu skilties numeriui (2 ir kt.). Jauniausios skilties numeris - nulis.

Bitas - vienos skilties dvejetainis skaičius (0 arba 1). Dvejetainis skaičius 11012 - keturių bitų skaičius.

Baitas - astuonių bitų dvejetainis skaičius, pvz. 110010012.

Zodis - dviejų baitų ilgio skaičius, pvz, sesioliktainis skaičius 7FB4h.

Desimtainė skaičiavimo sistema - skaičiavimo sistema turinti pagrindą 10. Ją sudaro 10 skaitmenų.

Sesioliktainė skaičiavimo sistema - skaičiavimo sistema turinti pagrindą 16. Ją sudaro 16 skaitmenų (0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F).

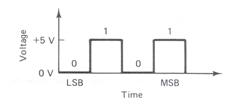

Maziausios (Least Significant Bit) ir didziausios (Most Significant Bit) vertės bitas - dvejetainio skaičiaus skiltys turinčios maziausią ir maziausią svorį, pvz. baite maziausią svorį (LSB) turi nulinė skiltis (20=1), o didziausią (MSB) - septinta skiltis (27=128).

Skaitmeninė sistema - sistema vykdanti operacijas tik su skaičiais ir diskretiniais dydziais. Skaitmeninė elektronika operuoja tik 1-niais ir 0-niais loginiais lygiais, t.y. sąvokomis įjungta (ON) ir isjungta (OFF). Mikroprocesoriuje visi duomenys yra isreiskiami "1" arba "0" ir veiksmai atliekami su skaičiais sudarytais tik is 1 ir 0 Desimtainė sistema naudojama rezultatams isvesti, nes prie jos yra pripratęs rezultatų vartotojas zmogus.

Informacija yra matuojama bitais, baitais (1 baitas = 8 bitams), kilobaitais (1 KB = 1024 B = 2 B), megabaitais (1 MB = 1024 KB = 2 B = 1.048.576B), gigabaitais (1 GB = 1024 MB = 2 B = 1.073.741.824B), ir t.t. Dvejetainėje sistemoje uzrasyti kodai yra labai ilgi ir dėl to nepatogūs. Mikroprocesoriuje duomenys gali būti 8, 16, 32 ir net 64 bitų ilgio, todėl skaičiams rasyti naudojamos patogesnės astuntainė ir sesioliktainė skaičių sistemos.

1 lentelė. Rysys tarp desimtainės ir dvejetainės skaičiavimo sistemų

|

Skaičius |

Skaičius |

Skaičius |

|||

|

Dvejetainis |

Desimtainis |

Dvejetainis |

Desimtainis |

Dvejetainis |

Desimtainis |

Dvejetainį skaičių, kaip ir bet kurį kitą, paversti desimtainiu galima sumuojant dėmenis, kuriuos sudaro skilties reiksmė padauginta is skaičiavimo sistemos pagrindo pakelto laipsniu, lygiu skilties numeriui.

Pavyzdziui:

Dvejetainis skaičius 110101112=

=1x2 +1x2 +0x2 +1x2 +0x2 +1x2 +1x2 +1x2

=1x128+1x64+0x32+1x16+0x8+1x4+1x2+1=21510

Pats didziausias skaičius, kurį galima sutalpinti į 8 dvejetaines skiltis į vieną baitą 11111111 . Skaičiai paprastai koduojami baitais, todėl, norint uzkoduoti didesnį skaičių, reikia naudoti daugiau baitų. Registrų ir atmintinių talpa matuojama baitais, kilobaitais, megabaitais, gigabaitais ir t.t.

Aritmetinių veiksmų vykdymo taisyklės tokios pačios, kaip ir dirbant su desimtainiais skaičiais, tačiau laikoma, jog kiekviena dvejetainio skaičiaus skiltis yra mazesnė uz 2 ir gali turėti tik dvi reiksmes - 1 arba 0:

Sudėtis 0 + 0 = 0; 1 + 0 = 1; 0 + 1 = 1; 1 + 1 = (perpildimas 1)0; 1 + 1 + 1 = (1)1.

Atimtis 0 - 0 = 0; 1 - 0 = 1; 0 - 1 = -1; 1 - 1 = 0.

Daugyba: 0 x 0 = 0; 0 x 1 = 0; 1 x 1 = 1.

Pavyzdziui:

Suma: Atimtis: Sandauga:

59 0011 1011 85 0101 0101 15 1111

+ 42 0010 1010 - 57 0011 1001 x 9 x 1001

101 0110 0101 28 0001 1100 135 1111 1111

10000111

Mikroprocesoriuje atimtis keičiama sudėtimi, pries tai neigiamą skaičių atitinkamai transformuojant į papildomą kodą, t.y. dvejetainių skaičių atimtis mikroprocesoriuje keičiama į turinio sudėtį su atėminio papildomu kodu. Papildomas kodas gaunamas neigiamo dvejetainio skaičiaus visas skiltis invertuojant (t.y. vienetus pakeičiant nuliais ir atvirksčiai) ir prie gauto skaičiaus jauniausios skilties pridedant 1. Pavyzdziui, skaičius "-3" būtų transformuojamas taip:

3 Inversija +1

1111 1100 1111 1101.

Tokia būdu atimties operacija mikroprocesoriuje atrodytų taip:

7 0000 0111

+1111 1101

4 1 0000 0100

Operacijos metu atsiradęs perpildymo vienetas rodo, kad rezultatas teigiamas. Jeigu pernesimo nėra - tai reiskia, kad atimties rezultatas neigiamas. Kai atėminio absoliutinė reiksmė didesnė uz turinio, gauname neigiamą rezultatą (t.y. nėra persipildimo is vyriausios skilties). Norint suzinoti neigiamo rezultato absoliutinę vertę, reikia gautą atimties rezultatą invertuoti ir prie jauniausios skilties pridėti 1.

Pavyzdziui: atlikime operaciją "4 - 15"; Raskime atsakymo absoliutinę vertę. Desimtainių skaičių atimtį (4 - 15) atitinka dvejetainių skaičių atimtis (0000 01002 - 0000 11112):

4 4 0000 01002

- 15 + 15 pap. kodas + 1111 00012

= 11 = 11 pap. kodas = 1111 01012

Matome, kad pernesimo is vyriausios skilties nėra, tai reiskia, kad gautas atimties rezultatas neigiamas. Gauname neigiamo skaičiaus 1111 01012 absoliutinį dydį:

Randame skaičiaus 1111 01012 inversiją - 0000 10102 ir prie jauniausios skilties pridedame +1. Gauname neigiamo dvejetainio skaičiaus 1111 01012 absoliutinį dydį 0000 10112 (dvejetainis) = 1110 (desimtainis).

2 lentelė. Rysys tarp dvejetainės, desimtainės ir sesioliktainės skaičiavimo sistemų

|

Dvejetainis |

Sesioliktainis |

Desimtainis |

Dvejetainis |

Sesioliktainis |

Desimtainis |

|

A | |||||

|

B | |||||

|

C | |||||

|

D | |||||

|

E | |||||

|

F |

Rasant programas mikroprocesoriams dazniausiai vartojama sesioliktainė skaičiavimo sistema. Verčiant dvejetainį skaičių į sesioliktainį, kiekvienas baitas padalinamas pusiau į dvi lygias dalis (tetradas) po 4 bitus. Tada kiekvieną tetradą sudarantis dvejetainis skaičius keičiamas jį atitinkančiu sesioliktainiu skaičiumi. Į pusę baito galima įrasyti dvejetainius skaičius nuo 0000 (desimtainis 0) iki 1111 (desimtainis 15).

Sesioliktainis 10 = desimtainiam 16. Kad jų nesumaisytumėm, sesioliktainiai skaičiai zymimi raide H(h), pavyzdziui: 10h = 16, arba 0Ah = 10, arba 0FFh = 255. Viename baite telpa du sesioliktainiai skaitmenys. Sesioliktainė sistema patogi tuo, kad sesioliktainis skaičius labai paprastai paverčiamas dvejetainiu ir atvirksčiai.

Dvejetainį skaičių paversti sesioliktainiu skaičiumi galima suskirstant dvejetainį skaičių į tetradas (pradedant jaunesniosiomis skiltimis) ir po to kiekvieną tetradą pakeisti ją atitinkančiu sesioliktainiu skaičiumi. Jeigu vyriausioje tetradoje yra maziau nei 4 skiltys, ją papildome nuliais. Pavyzdziui: dvejetainį skaičių 0100000010101011B pakeisti sesioliktainiu.

- dvejetainis

- skilčių svoriai

- sesioliktainis

Analogiskai sesioliktainis skaičius verčiamas į dvejetainį. Pavyzdziui: sesioliktainį skaičių B3D9h paversti dvejetainiu.

B 3 D 9 -

- skilčių svoriai

- dvejetainis

Veiksmai su sesioliktainiais skaičiais atliekami taip pat, kaip su desimtainiais, tik vienetas sumuojant pernesamas į vyresniąją skiltį tuomet, kai suma yra lygi arba didesnė uz 16.

Dvejetainis - desimtainis kodas (BCD - Binary Coded Decimal) dazniausiai naudojamas, kai reikia didelio tikslumo (reiksmių po kablelio), o taip pat informacijos atvaizdavimo įtaisuose, kadangi zmogus pripratęs prie desimtainės skaičiavimo sistemos (pvz.: priimtinesnė temperatūros indikacija 250 C, nei 000110010 C). Naudojant sį BCD kodą, kiekvienas desimtainis skaitmuo koduojamas atskirai 4 bitais, jam isreiksti naudojama tiek bitų, kiek jų reikia. Kadangi yra 16 keturių bitų kombinacijų, kai kurios jų nenaudojamos. Skaičius įrasytas viename baite atitinka dvi desimtainio skaičiaus skiltis. Pavyzdziui:

Susumuokime du BCD skaičius:

Dvej. skaičius BCD kodas

0000 0011 (=03h)

(=86h)

1000 1001 (=89h)

Kai kvarteto (tetrados) reiksmė virsija 9, rezultatą reikia koreguoti. Mikroprocesoriuose tai atlieka specialios komandos - DAA (Adjust After Addition), DAS (Adjust After Subtraction) ir kt. Pavyzdziui atliekant BCD kodų sudėtį:

Dvej. skaičius BCD kodas

0000 0111 (=07h)

+0000 1000 (=08h)

0000 1111 (=0Fh) Atliekama koregavimo po sudėties komanda DAA ir gauname:

0001 0101 (=15h)

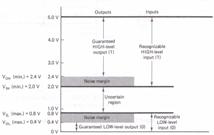

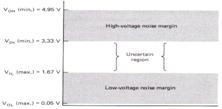

Visos elektroninės skaitmeninės schemos (tame tarpe ir mikroprocesorinės sistemos) sudarytos is skaitmeninių funkcinių blokų, kurių vidinę struktūrą sudaro baziniai loginiai elementai. Kiekvienas bazinis loginis elementas turi vieną ar kelis įėjimo isvadus ir vieną isėjimo isvadą. Panaudojant įvairias sių loginių elementų sujungimų kombinacijas ir skirtingą jų skaičių yra gaminamos mazos integracijos (Small Scale Integration - SCI) loginiai elementai, kombinacinės loginės schemos (Medium Scale Integration - MSI) ir mikroprocesoriniai įtaisai (Large Scale Integration - LSI ir Very Large Scale Integration - VLSI). Is esmės yra dvi pagrindinės skaitmeninių integrinių schemų seimos: TTL ir CMOS. Jos skiriasi savo eksploataciniais parametrais - darbo greičiu, sunaudojama galia, skaitmeninių loginių lygių (1 ir 0) įtampomis, apkrovimo galimybėmis ir kt. Visos auksčiau paminėtos schemos funkcionuoja veikiamos skaitmeninių signalų - 0 ir 1.

a) b)

c)

c)

3 pav. Skaitmeninių signalų savybės: a) skaitmeninio signalo pavyzdys; b) TTL signalo loginiai lygiai, c) CMOS signalo loginiai lygiai.

3 pav. iliustruoti TTL signalo ir CMOS signalo loginiai lygiai - t.y. įtampos, kurios atitinka loginį 1 ir 0. Matome TTL atveju (3,b pav.) įtampos nuo 0 V iki 0,8 V skaitmeninėje sistemoje traktuojamos kaip loginis 0, o įtampos diapazone nuo 2,4 V iki 5 V - kaip loginis 1. Tačiau kiekvienas is sių diapazonų suskyla į garantuotą (Guaranteed) ir triuksmingą (Noise Margin) zonas. Gamintojas garantuoja, kad skaitmeninės schemos į įtampas patenkančias į garantuotas zonas reaguos teisingai, t.y. kaip į atitinkamą loginį signalą. Jeigu skaitmeninio įtaiso įėjime veikia signalas, su amplitude is triuksmingos zonos - galimas klaidinga reakcija, kadangi bet kurioje skaitmeninėje schemoje veikia didesni ar mazesni triuksmai. Sie triuksmai sumuojasi su signalu ir bendra signalo įtampa gali patekti į neapibrėztą zoną ir skaitmeninio įtaiso reakcija tampa nevienareiksme. CMOS loginiai lygiai (3c pav.), kai maitinimo įtampa 5 V, siek tiek skiriasi - garantuotos zonos siauresnės - loginio 1 zona 4,95 - 5 V, o loginio 0 zona - 0 - 0,05 V. Tuo tarpu triuksmo zona gerokai platesnė uz TTL logikos.

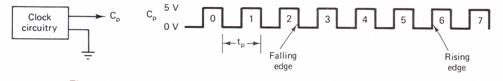

Dauguma skaitmeninių schemų reikalauja periodinių signalų sekos (4 pav.). Daznai tokia seka vadinama sinchronizacijos signalu, kurį apibūdina sie parametrai:

loginio vieneto įtampos lygis (+5 V, 4 pav.);

loginio nulio įtampos lygis (0 V, 4 pav.);

impulsų sekos periodas (tP) ir daznis (1/tP);

reikalavimai kylančio (Rising Edge) ir krintančio (Falling Edge) frontų trukmėms;

4 pav. Mikroprocesorinio įtaiso sinchronizacijos signalo pavyzdys

Mikroprocesoriniai įtaisai sudaryti is paprasčiausių loginių elementų. Loginių elementų veikimas aprasomas funkcijomis, kurios, kaip ir jų argumentai, gali įgyti dvi reiksmes: 0 ir 1. Sios funkcijos vadinamos loginėmis funkcijomis. Kintamojo reiksmės A ir inv A vaizdziai gali būti interpretuojamos fiziskai: isjungtas ar įjungtas jungiklis, zemas ar aukstas įtampos lygis laide.

Dvejetainio kintamojo reiksmes loginėse schemose atitinka loginio nulio ir loginio vieneto signalai. Mikroprocesorinėje technikoje naudojami sitokie elektrinių signalų lygiai įėjimuose: loginio nulio (zemo lygio) signalas < 0,8 V; loginio vieneto (auksto lygio) signalas > 2,0 V.

Daznai jie vadinami standartiniais TTL (tranzistorinės - tranzistorinės logikos) signalų lygiais.

Nors yra 16 skirtingų dviejų argumentų loginių funkcijų, bet loginių schemų realizacijai naudojamos tik kelios. Panagrinėsime svarbiausias is jų ir jas atitinkančius loginius elementus.

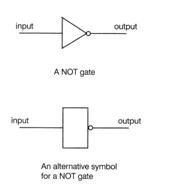

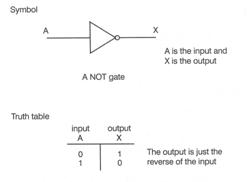

Elementas NE (invertorius) invertuoja argumento reiksmę (atlieka inversijos operaciją). Jei įėjimo signalo reiksmė lygi nuliui (nulio signalas), tai isėjimo signalo reiksmė lygi vienetui (vieneto signalas) ir atvirksčiai. Kintamojo A inversija uzrasoma invA. Inversija, skirtingai nuo kitų loginių funkcijų, yra vieno argumento funkcija. Loginis NE (NOT) elementas pavaizduotas 5 pav. Vienoje mikroschemoje jų gali būti nuo vieno iki sesiolikos (ir daugiau) elementų.

5 pav. Simbolinis loginio NE elemento zymėjimas ir jo darbo teisingumo lentelė

Elementas IR logiskai daugina argumentus (atlieka konjunkcijos operaciją): isėjimo signalo (funkcijos) reiksmė bus lygi vienetui (vieneto signalas) tik vieninteliu atveju, jei visų elemento įėjimų signalų (argumentų) reiksmės lygios vienetui. Įėjimo kintamųjų A ir B konjunkcija uzrasoma sitaip:

F=A B (dar vartojami zymenys AB, A B, A&B

Loginis IR (AND) elementas:

6 pav. Simbolinis loginio IR elemento zymėjimas ir jo darbo teisingumo lentelė

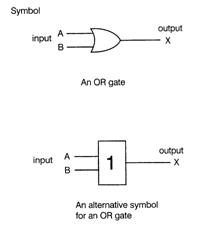

Elementas ARBA logiskai sudeda argumentus (atlieka disjunkcijos operaciją): isėjimo signalo reiksmė bus lygi vienetui, jei bent vieno is jo įėjimų signalo reiksmė lygi vienetui. Disfunkcija uzrasoma sitaip:

F= A B (arba A+B).

Loginis ARBA (OR) elementas:

7 pav. Simbolinis loginio ARBA elemento zymėjimas ir jo darbo teisingumo lentelė

Konjunkcijos, disjunkcijos ir inversijos loginės funkcijos sudaro pilną funkcijų sistemą, vadinamąją Būlio bazę, nes su siomis funkcijomis galima isreiksti bet kokio sudėtingumo loginę funkciją.

Loginis Suma moduliu 2 (XOR) elementas:

8 pav. Simbolinis loginio Suma M2 elemento zymėjimas ir jo darbo teisingumo lentelė

Loginių elementų darbo pavyzdziai

9 pav. Dviejų skaičių loginė sandauga panaudojant loginius IR elementus

![]()

.....

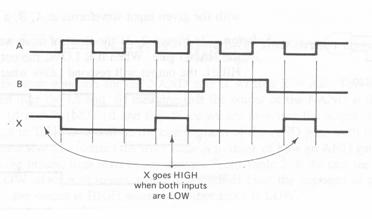

10 pav. Laikinės diagramos loginio elemento ARBA-NE įėjimuose ir isėjimuose

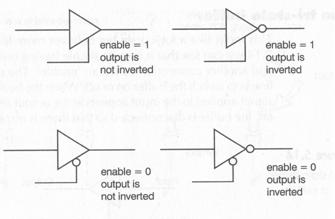

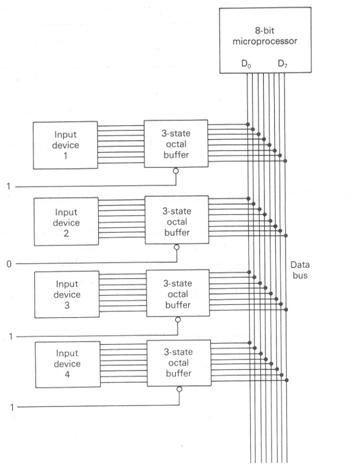

Tribūviai buferiniai elementai mikroprocesorinėse sistemose daznai naudojami duomenų magistralėse, prie kurių prijungti keli informacijos perdavimo įtaisai. Naudojant specialius duomenų perdavimo leidimo signalus Enable vienu metų prie magistralės prijungiamas tik vienas informacijos perdavimo įrenginys. Kiti įrenginiai, kurių leidimo signalas neaktyvus, elektriskai atjungti nuo magistralės. Is zemiau pateikiamo pavyzdzio matome, kad leidimo signalo (Enable) aktyvus lygis gali būti ir 0-nis, ir 1-nis. Buferiniai elementai gali būti invertuojantis ir neinvertuojantis įėjimo signalą.

11 pav. Simbolinis tribūvių buferinių elementų zymėjimas

Tribūvių buferinių elementų panaudojimo pavyzdys, iliustruojantis keturių duomenų įvedimo prietaisų prijungimą prie mikroprocesorinės sistemos duomenų magistralės. Pavyzdyje panaudoti tribūviai 8 skilčių magistralės buferiai, kurių aktyvus leidimo signalas - nulinio lygio. Pavyzdyje parodytas duomenų įvedimo is 2-ojo įtaiso - antrojo prietaiso isėjimo buferį is "trečios būsenos" į aktyvią perveda leidimo signalo 0-inis lygis. Naudojant tokį schemotechninį sprendimą, valdymo grandinės (parastai tai atlieka adresų desifratorius") turi uztikrinti, kad vienu metu būtų tik vienas isrinkimo signalas. Priesingu atveju bus aktyvus keli buferiniai elementai ir informacija bus nuskaitoma is magistralės su klaidomis.

12 pav. Tribūvių buferinių elementų panaudojimo pavyzdys mikroprocesorinėje sistemoje

Kompiuteriai yra sudaryti is tūkstančių paprasčiausių loginių elementų. Jų atliekamos funkcijos yra sudėtingesnių funkcijų sudedamoji dalis, o tas sudėtingesnes funkcijas realizuoja tipinės funkcinės schemos - operaciniai įtaisai, sudaryti is loginių elementų. Tuos įtaisus pramonė gamina kaip vidutinės integracijos schemas. Operacinis įtaisas, kurio isėjimo signalas priklauso tik nuo įėjimų signalų reiksmių nagrinėjamuoju momentu, vadinamas kombinaciniu. Mikroprocesorinėse sistemose plačiausiai naudojami sie kombinaciniai operaciniai įtaisai: desifratoriai, multiplekseriai, programuojamos loginės matricos, sumatoriai, magistraliniai buferiai, koderiai, dekoderiai ir kt. Operacinis įtaisas, kurio isėjimo signalai priklauso ne tik nuo įėjimų signalų reiksmių, bet ir nuo jo vidinės būsenos, vadinamas sekvenciniu. Tai - trigeriai, registrai, skaitikliai.

Operaciniai įtaisai operuoja ir su tiesioginiais, ir su inversiniais kintamaisiais. Tiesioginį kintamąjį atitinkantį signalą vadinsime aktyviu teigiamu, o inversinį kintamąjį - aktyviu neigiamu (aktyviu vadinamas loginis signalas, į kurį reaguoja loginė schema, t. y. keičiasi jos būsena, o pasyviu - kuris schemos būsenos nekeičia).

Trumpai susipazinsime su plačiausiai naudojamais operaciniais įtaisais.

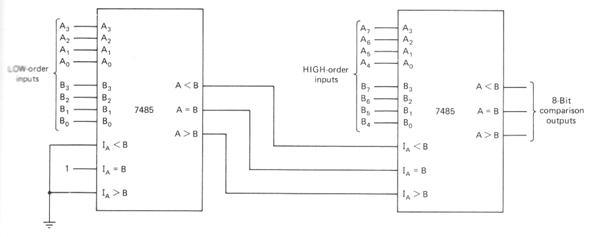

Skaitmeniniai komparatoriai (kodų palyginimo schemos) mikroprocesorinėse sistemose panaudojami isorinio įtaiso isrinkimo signalo formavimui, kai adresų magistralėje esantis kodas sutampa su įtaisui suteiktu adresu mikroprocesorinės sistemos adresų erdvėje. Kai kodai sutampa, formuojamas aktyvaus loginio lygio signalas isėjime "A=B" (zr. 13 pav.). Taip pat komparatoriai panaudojami prioritetinėse schemose, siekiant nustatyti, kurio aptarnavimo prasančio įrenginio prioritetas yra aukstesnis (14 pav.).

13 pav. Skaitmeninis komparatorius

14 pav. Skaitmeninio komparatoriaus panaudojimo pavyzdys

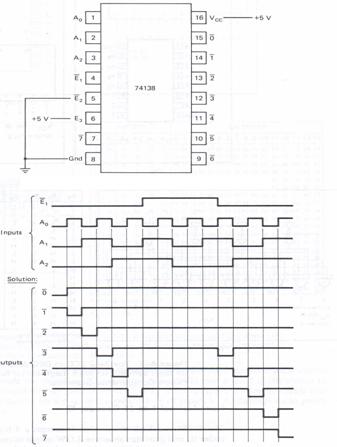

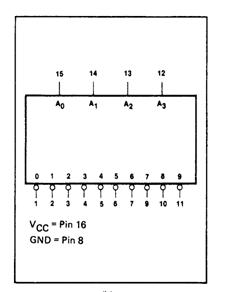

Desifratorius (Decoder keičia įėjimų signalų rinkinį (dvejetainį kodą) į signalą tik viename is isėjimų. Desifratorius turi n įėjimų ir 2n isėjimų. Signalas atsiranda tik viename isėjime - tame, kurio numeris atitinka įėjimų skaičių rinkinį, pavyzdziui, dvejetainį kodą 010 įėjime atitinka isėjimo signalas 00000 00 (arba 11, priklausomai nuo to, koks aktyvus isėjimo signalo lygis) - antrame isėjime yra vieneto (nulio) signalas. Desifratoriai paprastai naudojami kartu su registrais ar skaitikliais ir transformuoja juose saugomus kodus.

Desifratoriai mikroprocesorinėse sistemose kartu su adresų desifratoriumi naudojami įtaisų prijungtų prie duomenų magistralės isrinkimo (leidimo) signalų formavimui (pvz., sistemoje kuri pavaizduota 12 pav.). Desifratoriai taip pat daznai panaudojami ir informacijos indikacijos schemose, kai naudojama dinaminė indikatorių valdymo sistema, t.y. vienu metu gali būti isrinktas tik vienas indikatorius ir indikatoriai atvaizduoja informaciją atliekant cikliską jų isrinkimą. Zmogaus akis yra inertiska ir jam atrodo, kad vienu metu sviečia visi indikatoriai. Taip taupomas energijos sunaudojimas ir sumazėja schemą sudarančių mikroschemų kiekis.

Desifratoriai gali būti dvejetainiai (15 pav.) ir dvejetainiai - desimtainiai (BCD, 16 pav.). Dvejetainiai desifratoriai reaguoja (desifruoja) visas galimas dvejetainio kodo kombinacijas. Dvejetainiai - desimtainiai desifratoriai reaguoja (suaktyvina vieną is isėjimų) tik reaguodami į įėjime esantį dvejetainį kodą, kuris yra nedidesnis uz 1001B. Įėjime esant didesniam kodui, nei viename desifratoriaus isėjime nėra aktyvaus signalo.

15 pav. Dvejetainis desifratorius, jo darbo laikinės diagramos bei darbo teisingumo lentelė

16 pav. Dvejetainis desimtainis (BCD) desifratorius ir jo darbo teisingumo lentelė

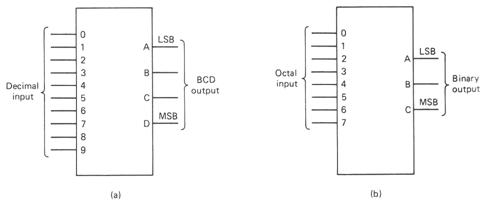

Sifratoriai (Coder isėjime suformuoja dvejetainį kodą to įėjimo, kuriame yra aktyvus signalo lygis. Kiekvienam įėjimui suteikiamas prioritetas, t.y. jeigu vienu metu aktyvūs loginiai lygiai atsiranda keliuose įėjimuose, tai sifratoriaus isėjime bus auksčiausią prioritetą turinčio įėjimo kodas. Mikroprocesorinėse sistemose naudojami dvejetainiai ir dvejetainiai desimtainiai - BCD sifratoriai. Prie sifratorių isėjimų gali būti jungiami specialūs skystųjų kristalų įtaisai (LCD), kurie atvaizduoja sifratoriaus isėjime esantį kodą.

17 pav. BCD (a) ir dvejetainis (b) sifratoriai

18 pav. BCD sifratorius ir jo darbo teisingumo lentelė

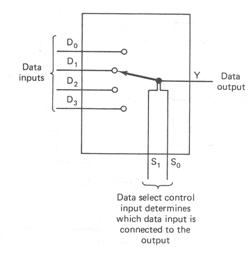

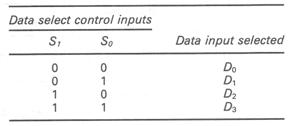

Multiplekseris perduoda signalą is įėjimo, kurio numeris nurodomas dvejetainiu kodu adreso įėjimuose į isėjimą. Jo veikimo principą geriausiai iliustruoja struktūra, parodyta 19 pav. Multiplekseriai, kurie kartais vadinami komutatoriais, ar selektoriais, naudojami kelių signalų saltiniams sujungti arba loginėms funkcijoms realizuoti.

19 pav. Keturių linijų skaitmeninio multiplekserio funkcinė schema ir teisingumo lentelė

Skaitmeninių signalų multiplekseriai mikroprocesorinėse sistemose dazniausiai naudojami įvedimo - isvedimo įtaisuose, įvedant (apjungiant) skaitmeninius signalus is kelių informacijos perdavimo saltinių (18 pav.).

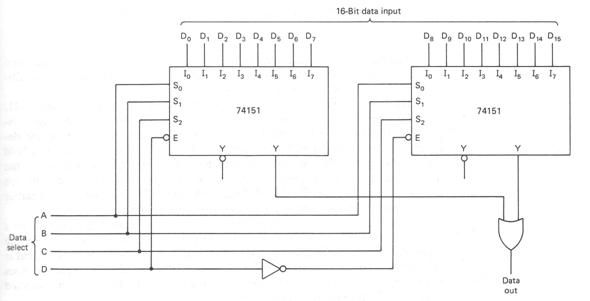

20 pav. 16 linijų multiplekseris

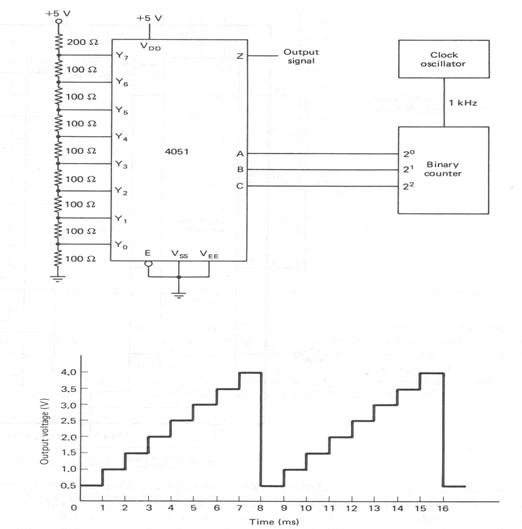

Gana plačiai mikroprocesorinėse sistemose naudojami analoginių signalų multiplekseriai (21 pav.), kadangi realiame pasaulyje analizuojama informacija dazniausiai būna analoginė. Į analoginių signalų multiplekserio įėjimus patenka informacija is įvairių jutiklių ar kitų analoginių signalų saltinių.

21 pav. Analoginių signalų multiplekseris

Multiplekserio isėjimas paprastai prijungiamas prie analoginio skaitmeninio keitiklio (ASK), keičiančio analoginę informaciją į dvejetainį kodą, įėjimo. Analoginio signalo įėjimo isrinkimas valdomas skaitmeninių kodu, kurį formuoja valdymo įtaisas, pavyzdziui mikroprocesorius ar mikrovaldiklis. Svarbūs analoginio multiplekserio parametrai:

įėjimo signalų dinaminis diapazonas (nuo kelių mV iki desimčių V);

atviro kanalo varza (nuo kelių iki simtų omų);

maksimali įėjimo signalo įtampa;

įtampos keitimo į skaitmeninį laikas;

analoginių įėjimų skaičius;

analoginio kanalo isrinkimo signalų loginiai lygiai;

vidinio buferio kodams saugoti dydis;

skaitmeninio isėjimo tipas (nuoseklus arba lygiagretus) ir kt.

Siuolaikiniuose mikrovaldikliuose analoginių signalų multiplekseriai dazniausiai būna integruoti į patį mikrovaldiklį. Analoginių signalų multiplekseriai gali būti panaudojami ir įvairios formos skaitmeniniu būdu valdomų analoginių signalų formavimui (22 pav.). Siame pavyzdyje analoginių signalų multiplekseris panaudotas piūklinės įtampos formavimui.

22 pav. Analoginių signalų multiplekserio panaudojimo pavyzdys

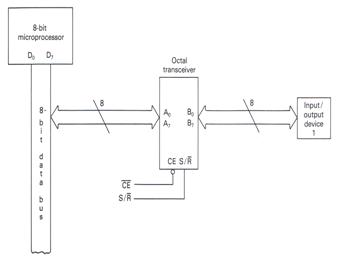

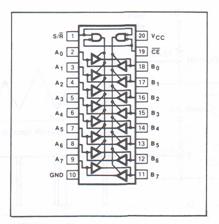

Magistralės buferiai mikroprocesorinėse sistemose naudojami kaip buferiniai elementai tarp duomenų magistralės ir įvedimo-isvedimo įrenginio. Buferių isėjimai tribūviai ir jų valdymui naudojami leidimo signalai CE (Crystal Enable). Magistralės buferiai būna vienkrypčiai ir dvikrypčiai (pvz., 23 pav.). Dvikrypčiuose buferiuose be isrinkimo signalo CE dar naudojamas informacijos perdavimo kryptį valdantis signalas S/R (23 pav.).

23 pav. Astuonių skilčių dvikryptis magistralės buferis ir jo panaudojimas MPS

Dvikryptis magistralės buferis naudojamas, kada prie duomenų magistralės prijungtas universalus periferinis įrenginys, galintis ir perduoti, ir priimti informaciją is mikroprocesoriaus. Tuo atveju, kai prie duomenų magistralės prijungtas tik siunčiantis informaciją įtaisas, naudojamas vienkryptis magistralės buferis (24 pav.).

24 pav. Astuonių skilčių vienkryptis magistralės buferis ir jo panaudojimas MPS

24 paveikslėlyje pateiktas vienkryptis duomenų magistralės buferis turi du leidimo įėjimus OE1 ir OE2 (Output Enable). Jie gali būti valdomi atskirai arba sujungti į tarpusavyje, kaip 24 pav. Bet kuriuo atveju duomenys is periferinio įrenginio pateks į duomenų magistralę, tiktai tada, kai abu leidimo signalai bus zemo loginio lygio.

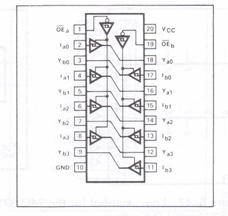

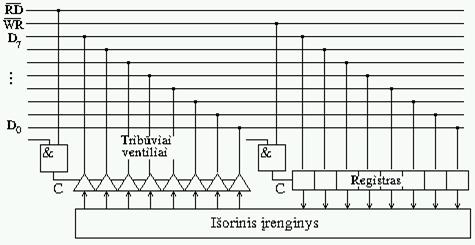

Buferiniai registrai Periferiniuose įrenginiuose, į kuriuos informacija tik isvedama naudojami buferiniai registrai. Duomenys is duomenų magistralės gali būti uzfiksuojami vidiniuose buferinių registrų trigeriuose teigiamu, arba neigiamu impulso C frontu (25 pav., b). 26 pav. pateikta tokio buferinio registro vidinė sandara. Kito tipo buferiniuose registruose duomenys perduodami is duomenų magistralės į periferinį įrenginį esant aktyviam leidimo signalo lygiui. Pavyzdyje (25 pav, a) aktyvus leidimo signalo lygis - aukstas. Abu registrai (25 pav.) turi isėjimo leidimo signalą OE (Output Enable) - zemas aktyvus lygis. Kai sis signalas auksto loginio lygio, registrų isėjimai Q0 - Q7 pervedami į trečią neaktyvią būseną.

a) b)

25 pav Astuonių skilčių buferiniai registrai

26 pav. pavaizduotas buferinis registras turintis dinaminį duomenų įrasymo įėjimą. Duomenys įėjime keičiasi tik po teigiamo signalo fronto siame įėjime. Auksto loginio lygio signalas įėjime EI perveda buferinio registro isėjimus į "trečią" neaktyvią būseną.

26 pav. Buferinis registras su dinaminiu duomenų įrasymo įėjimu

27 pav. pateikiamas buferinių registrų panaudojimo MPS pavyzdys. Siame pavyzdyje jie panaudoti duomenų perdavimui į du informacijos isvedimo prietaisus. Registrų isėjimai visada aktyvioje būsenoje - jų įėjimai OE įzeminti. Informaciją keičiasi registrų isėjimuose nuo signalų C1 ir C2 teigiamų frontų.

27 pav. Buferiniai registrai mikroprocesorinėje sistemoje

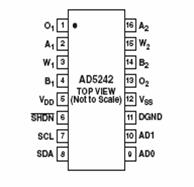

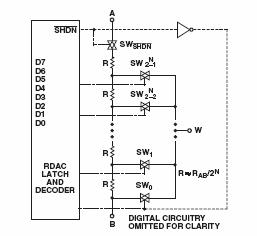

Siuolaikinėse elektroninėse schemose sutinkami ir mechaniniai ir skaitmeniniai potenciometrai. Jų dazniausiai atliekamos funkcijos yra įtampos dalinimas arba mazinimas, filtrų suderinimas ir kitos. Vystantis gamybos technologijoms atsirado ir skaitmeniniai potenciometrai. Abiejų tipų potenciometrai turi privalumų ir trūkumų. Aptarsime dviejų tipų potenciometrus: mechaninius ir skaitmeninius. Skaitmeniniai potenciometrai gaminami remiantis silicio technologijomis, kurios naudojamos analoginėms arba skaitmeninėms integrinėms schemoms. Skaitmeniniai potenciometrai atlieka tokias pačias fundamentalias operacijas kaip ir mechaniniai potenciometrai. Skaitmeniniai potenciometrai turi vieną akivaizdų pranasumą: slankiklio vietą galima nurodyti programiskai. Sią funkciją lengvai gali atlikti mikrovaldiklis. Panagrinėsime Analog Device mikroschemą AD5242, kurioje įmontuoti du skaitmeniniai potenciometrai. Kiekvieno potenciometro slankiklio vietą (256 pozicijos) galima programiskai nurodyti. Reguliuojamas potenciometras valdomas naudojant I2C sąsają. Taip nustatoma varza tarp isvadų A ir W ir tarp W ir B gnybtų.

37 pav. Mikroschemos AD5242 blokinė schema ir korpusas

Skaitmeninis potenciometro slankiklis turi 256 pozicijas. Nustatant varzą tarp isvadų W ir B, siunčiami astuoni bitai į registrą RDAC, kurie nurodo konkrečią slankiklio vietą. Minimalią varzą tarp isvadų W ir B sudaro slankiklio varza 60 Ω. Tokiu atveju į registrą RDAC turi būti nusiųstas skaičius 0h. Sekančioje slankiklio pozicijoje varza tarp W ir B lygi 99 Ω (RWB = RAB/256 + RW = 39 + 60). RDAC registras pavaizduotas 38 pav.

38 pav. RDAC registro schema

Varzos vertė tarp gnybtų W ir B isreiskiama formule.

![]()

čia: D - desimtainis skaičius nuo 0 iki 255, kuris siunčiamas į RDAC registrą, RAB - potenciometro varzos nominali vertė, RW - slankiklio varza (60 Ω), RWB - norimas varzos nominalas.

Varza tarp isvadų W ir A tai pat nustatomas skaitmeniniu būdu per I2C sąsają. Nustatomos varzos vertė RWA isreiskiama formule:

![]()

Kiekvienas mikroprocesorinės sistemos funkcinis blokas yra sudėtinga elektroninė schema, todėl jas nagrinėsime atskirai. Pradėsime nuo pagrindinio ir sudėtingiausio bloko - mikroprocesoriaus.

Vystantis mikroelektronikai viename kristale tilpo vis sudėtingesnes funkcijas atliekančios schemos. Įranga su jomis darėsi vis patikimesnė, bet mazėjo mikroschemų universalumas. Pagrindinės sąnaudos mikroschemų gamyboje yra technologijos paruosimas. Todėl mazomis serijomis gaminti specializuotas mikroschemas buvo brangu. Gamybos masiskumui padidinti ir atpiginti buvo sukonstruotos programuojamos universalios mikroschemos - mikroprocesoriai (mP). Pirmąjį 4 bitų mP 4004 (2226 tranzistoriai) 1971 m. sukonstravo firma "Intel". Jis sugebėjo valdyti 4096 keturių bitų ilgio adresus, vykdė 45 skirtingas instrukcijas. Tais pačiais metais "Intel" pagamino 8 bitų mP 8008, kuris galėjo valdyti 16 KB atmintinę ir vykdė jau 48 instrukcijas. 1973 m. "Intel" pagamino pirmąjį moderniską 8 bitų mP 8080 (4600 tranzistoriai), kuris buvo 10 kartų spartesnis, valdė 64 KB atmintinę ir vykdė daugiau instrukcijų. Tuo metu ir kitos firmos pradėjo gaminti savos konstrukcijos mP, pavyzdziui, 1974 m. MC6800 (Motorola), 1976 m. Z80 ("Zilog"). 1978 m. Firma "Intel" pagamino 16 bitų mP 8086, o 1979 m. kiek paprastesnį mP 8088 (30000 tranzistorių), o "Zilog" - mP Z8001. Jie valdė 64 KB atmintnę, turėjo daugiau vidinių registrų, buvo dar spartesni. 1980 m. "Motorola" pradėjo gaminti mP MC68000. 1983 m. buvo pradėti gaminti dar tobulesni 16 bitų mP: 80286 (134000 tranzistorių), MC68010, Z8003. mP taip pat gamino firmos "Hewlett-Packard", "Bell Laboratories", "National Semiconductor" ir kitos. 1987 m. "Intel" pagamino 32 bitų mP 80386 (276000 tranzistorių), 1989 m. - sudvejintą, turintį vidinę RAM mP 80486 (1200000 tranzistorių), 1993 m. - mP "P5" (3000000 tranzistorių), 1995 m. - mP "P6" (apie 5000000 tranzistorių). 1998 m. buvo pradėtas gaminti "Pentium II", kurio darbo daznis buvo 450 MHz, 2000 m. pavasarį - 800 MHz "Pentium III" (22000000 tranzistorių), o rudenį buvo pasiektas ir virsytas 1 GHz daznis. 2003 m. pavasarį - 3 GHz "Pentium 4" (42 x106 tranzistorių), o pabaigoje 3,2 GHz "Pentium 4 EE" (178 x106 tranzistorių). AMD pradėjo gaminti naujos kartos 32/64 bitų procesorių "Athlon 64" (106x106 tranzistorių).

Dabar daug firmų gamina įvairios paskirties mP. Be bendrosios paskirties mP gaminami signalų procesoriai (DSP - Digital Signal Processor) skirti signalų analizei bei jų apdorojimui. Jie yra mobilaus rysio telefono aparatuose, garso plokstėse. Gaminami specialūs grafiniai procesoriai greitai piesiantys monitoriuje sudėtingus 2D ir 3D vaizdus, taip pat muzikiniai procesoriai (PSG - Programmable Sound Generator). Neįtikėtinai sparčiai didėja mP veikimo sparta. Taktinis daznis, buvęs simtai kHz, jau artėja prie 4 GHz, o tranzistorių skaičius - simtų milijonų kristale. Tobulėja mP struktūra ir dabar jie jau sugeba per vieną taktą atlikti keletą operacijų, valdyti gigabaitines atmintines. Toje pačioje mikroschemoje gali būti keli procesoriai (pvz., keli pagrindiniai ir matematiniai), trys spartinančiosios (Cache) operatyviosios atmintinės ir jų valdymas. Jiems gaminti naudojamos 0,13 mm ir 0,09 mm technologijos. Rengiamasi įsisavinti 0,06 mm technologiją.

Visų mP veikimo principas panasus. mP naudojantys sudėtingas, nevienodo ilgio komandas vadinami CISC (Complex Instruction Set Computer), o mP naudojantys paprastesnes, vienodo ilgio komandas - RISC (Redused Instruction Set Computer). RISC mP geresni tuo, kad nereikia perduoti papildomų duomenų apie instrukcijos ilgį. Atmintinė gali būti valdoma segmentais (8086, 8088) arba tiesiogiai. Pirmasis būdas labai patogus, kol programa telpa į segmentą (pvz., 16 bitų mP segmentą sudaro 64 KB). Kai atmintinė valdoma tiesiogiai (MC680..) programuojant nereikia galvoti apie segmento dydį.

Modernieji mP yra labai sudėtingi, todėl apie juos pakalbėsime pabaigoje. mP veikimą ir programavimą aiskinsimės nagrinėdami paprastesnius klasikinius mP. Labai spartūs ir sudėtingi mP reikalingi tik labai sudėtingiems MĮ (pvz., zaidimų, asmeniniams kompiuteriams, serveriams bei superkompiuteriams).

Jie yra labai įvairūs ir priklauso nuo mP paskirties. Charakterizuojant daugumą mP yra nurodomi sie parametrai:

Mikroprocesoriaus tipas (universalus, specializuotas).

Duomenų zodzio ilgis (vidinis/isorinis) bitais (4, 8, 16/8, 32/16, 64/32). Pavyzdziui, mP 386SX turėjo 32 bitų vidinę ir 16 bitų isorinę duomenų magistrales.

Adresuojamos atmintinės dydis baitais (pvz., 8088 - 1 MB, 80286 - 16 MB, 80386 - Pentium - 4 GB).

Taktinis darbo daznis MHz (vidinis/isorinis). Pavyzdziui, 80486DX2 80/40 reiskia, kad mP dirba 80 MHz dazniu, o su aplinka bendrauja 40 MHz dazniu.

Veikimo sparta dazniausiai nusakoma operacijų per sekundę skaičiumi (MIPS - Millions Instructions per Second). Sis parametras priklauso ir nuo komandų sudėtingumo.

Gamybos technologija (p-MOP, n-MOP ,...).

Elektriniai parametrai: suvartojamoji galia (iki 100 W), maitinimo įtampos, srovės.

Konstrukciniai parametrai: dydis, kojelių skaičius, jų isdėstymas, tvirtinimas ir t.t.

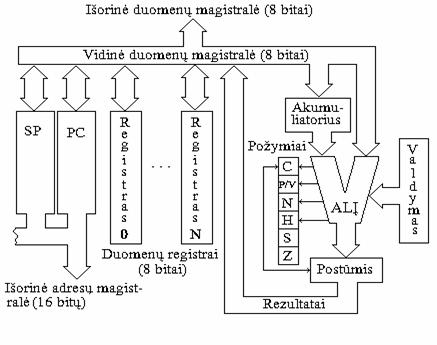

mP susideda is trijų pagrindinių dalių: aritmetinio loginio įtaiso (ALĮ), angliskai jis vadinamas ALU (Aritmetic Logic Unit), registrų ir valdymo bloko. Visi mP įtaisai tarpusavyje yra sujungti vidinėmis duoenų (VDM) ir adresų (VAM) bei valdymo signalų (VVM) magistralėmis. Duomenų magistrale abiem kryptimis cirkuliuoja duomenys ir adresai, o adresų magistrale - tik adresai is mP į jo isorę. Valdymo signalai is valdymo įtaiso siunčiami į visus mP įtaisus, į mP isorę bei priimami is isorės. mP yra ir daugiau įtaisų. VDM laidų skaičius nusako mP zodzio ilgį bitais. Kokias operacijas gali atlikti ALĮ, kiek, kokių ir kokios talpos registrų yra mP, taip pat valdymo įtaiso sudėtingumas priklauso nuo konkretaus mP konstrukcijos.

mP veikimą valdo ROM arba RAM esanti programa. Įjungus maitinimą, pradeda veikti taktinių impulsų generatorius, sinchronizuojantis viso MĮ darbą. Pirmoji komanda isvalo mP programos skaitiklį ir perjungia į pradinę būseną visus MĮ elementus. Kita komanda įraso į sį skaitiklį adresą, nurodantį ROM ląstelę, kurioje yra MĮ paleidimo programos pirmoji instrukcija. Sis adresas yra numatytas konstruojant MĮ. Toliau MĮ tikrina ir paruosia darbui ROM esanti programa. Paleidusi mikroprocesorinį įtaisą, ROM esanti programa, jo valdymą gali perduoti programai, kuri yra RAM.

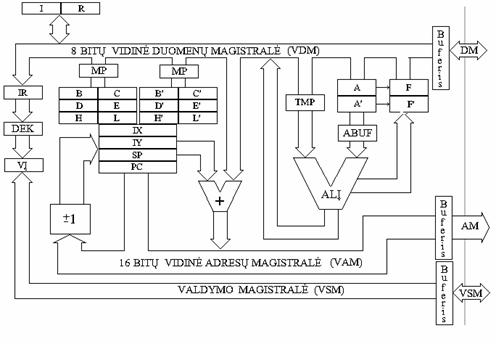

Panagrinėsime savo metu labai populiaraus astuonių bitų mP Z80 sandarą (39 pav.). Astuonių bitų mP duomenų magistralę sudaro astuoni laidai. mP taip pat yra valdymo signalų ir 16 bitų adresų magistralės. Nuo adresų magistralės pločio priklauso tiesiogiai adresuojamos atmintinės talpa.

39 pav. 8 bitų mikroprocesoriaus standartinė struktūra

ALĮ atlieka aritmetines ir logines operacijas. Viename jo įvesčių yra specialus registras akumuliatorius. Akumuliatorių gali būti ir daugiau. ALĮ duomenis gali paimti tiesiog is VDM ir is akumuliatoriaus (A). Jis, priklausomai nuo atliekamos operacijos, operuoja vienu arba dviem zodziais. Pavyzdziui, sudėčiai reikalingi du zodziai (A + B), o inversijai - vienas. Operacijos, kurias gali atlikti ALĮ, priklauso nuo mP tipo. Dazniausiai jis atlieka sudėties, atimties, loginės sandaugos, postūmio, padidinimo ir sumazinimo vienetu bei daugybos operacijas. Duomenys į ALĮ patenka per buferinius registrus - kaupykles (40 pav.). Operacijos rezultatas dazniausiai saugomas akumuliatoriuje.

40 pav. Mikroprocesoriaus Z80 struktūra

mP yra bendrieji ir specialieji registrai. Bendrieji registrai palengvina programuotojo darbą ir pagreitina MĮ veikimą, nes, esant vidinei atmintinei, mP tenka rečiau kreiptis į isorę. Specialieji registrai yra būtini mP veikimui ir neprieinami programuotojui. Beveik visuose mP yra sie specialieji registrai: akumuliatorius, atmintinės adreso, komandų, pozymių, buferiniai registrai ir programos skaitiklis.

Specialieji registrai

Pagrindinis mP registras vadinamas akumuliatoriumi (A). Jis naudojamas atliekant daugumą aritmetinių ir loginių operacijų. Duomenys pirmiausia įrasomi į akumuliatorių ir tik po to perduodami į ALĮ. Kitas zodis į ALĮ perduodamas per buferinį registrą (kaupyklę) is VDM. Akumuliatoriuje zodį galima perstumti, invertuoti ir atlikti kitus veiksmus su duomenimis.

Programos skaitiklyje (PC - Program Counter) visada yra komandos adresas, kurią mP ruosiasi vykdyti. Pries pradedant vykdyti komandą, adresas adresų magistrale siunčiamas į MĮ atmintinės valdymo schemą. Atmintinės valdymo schema perskaito adrese nurodytos ląstelės turinį ir jį duomenų magistrale siunčia į mP valdymo bloko komandų registrą IR (40 pav.). Valdymo bloko desifratorius (DEK) dekoduoja komandą ir pradeda ją vykdyti. Pasiuntus komandos adresą, adresų skaitiklis prideda prie PC registro adreso vienetuką. Kai komandą sudaro keli baitai, registras laukia nurodymo pasiųsti kitos komandos arba kito baito adresą. 40 pav. parodyto mP adresą sudaro 16 bitų, todėl jis gali tiesiog kreiptis į 65536 (216) baitų (8 bitų ląstelių) = 65536/1024 = 64 KB talpos atmintinę.

Į steko rodiklio registrą (SP - Stack Pointer) yra įrasomas steku vadinamos atmintinės dalies pradzios adresas. Steke įrasomi adresai, kur ieskoti pertrauktos vykdyti programos duomenų, adresai į kuriuos reikia grįzti įvykdzius paprogramę ar pertraukimą. PC ir SP registrai yra 16 skilčių. Jie sujungti su vidine adresų magistrale.

Postūmio registras gali būti ALĮ įvestyje arba isvestyje. Jis perstumia bitą į kairę arba į desinę per vieną ar daugiau skilčių. Perstūmimu galima atlikti daugybos veiksmą.

Pozymių registre (F - Flag) indikuojami tam tikri rezultato pozymiai, pavyzdziui, jis lygus ar nelygus nuliui, jis teigiamas ar neigiamas ir pan. Jie naudojami valdymui. Pavyzdziui, mP Z80 pozymių registro skiltyje C (39 pav.) saugomas operacijos metu atsiradęs perpildymo bitas. Jis atsiranda, kai rezultatas nebetelpa į 8 bitus arba perstumiant zodį. Vienetas skiltyje P/V gali reiksti skilties perpildymą, kai atliekamos aritmetinės operacijos, arba, atliekant logines operacijas, rodyti, kad skiltyje yra lyginis vienetų skaičius. Skiltis N skirta nurodyti, kokia operacija sumavimas ar atimtis yra vykdoma. Skiltyje H nurodoma ar buvo pernesimas is zemesniosios skilties į aukstesniąją. Vienetukas skiltyje S rodo, kad baitas yra neigiamas, o nuliukas skiltyje Z, kad operacijos rezultatas yra 0.

ALĮ įvestims atskirti nuo isvesties naudojami buferiniai registrai - kaupyklės, kur laikinai saugomi is magistralės paimti duomenis. Dazniausiai jie yra ALĮ įvestyse (pvz., TMP ir A registrai, 40 pav.). Jie neleidzia VDM esantiems signalams susimaisyti.

Pertraukimams valdyti skirtas registras I. Registras R generuoja signalus MĮ operatyviojoje atmintinėje (RAM) įrasytai informacijai regeneruoti.

Bendrieji registrai

Visus juos galima naudoti kaip vidinę atmintį, kai kurie jų gali atlikti akumuliatoriaus funkcijas.

mP Z80 astuonių bitų registrai B, C, D, E, H, L (40 pav.) naudojami akumuliatoriui skirtiems duomenims įsiminti. Kadangi kreipimosi laikas į vidinius registrus yra daug trumpesnis uz kreipimosi laiką į MĮ atmintinę, juos protingai panaudojant galima paspartinti programos veikimą. Pavyzdziui, skaičiuojant ciklą, juose laikyti tarpinius rezultatus ir tik galutinį rezultatą perrasyti į MĮ atmintinę. B registras yra specifinis. Jį galima naudoti skaičiuojant ciklą. Kai kuriuos sių registrų galima sujungti poromis ir naudoti, kaip 16 bitų registrus. Tai poros AF, BC, DE, HL. Registrų B ir HL kombinacija tampa dvigubu akumuliatoriumi. mP Z80 yra minėtų registrų dubleriai B', C', D', E', H', L', taip pat A' - akumuliatoriaus dubleris.

IX ir IY yra indekso registrai. Juose dazniausiai saugomas skaičius, prie kurio V pavidalo blokelis su "+" norimu atstumu perstumia adresą pridėdamas baitą is VDM.

Mikroprocesorių registrų struktūros skiriasi (41 pav.)

|

41 pav. mP 8080 (a), MC 6800 (b),

Z80 (c) registrų struktūros |

Valdymo schemos (40 pav.) sinchronizuoja visų mP mazgų darbą. Joms priklauso komandų registras (IR - Instruction Register), komandų desifratorius (DEK) ir valdiklis (V) valdantis mP. Į komandų registrą įrasoma is MĮ atmintinės paimta vykdyti komanda. Komandų dekoderis sią komandą issifruoja ir siunčia signalus valdikliui, kuris valdo komandos vykdymą mP ir jo isorėje.

Vidinė duomenų magistralė naudojama duomenims perduoti, ji sujungia ALĮ su visais mP registrais. Tik gavęs atitinkamą signalą, registras gali paimti arba perduoti duomenis į VDM. Pavyzdziui, sudedant akumuliatoriaus ir registro D turinius, pirmuoju taktu akumuliatoriaus turinys siunčiamas į akumuliatoriaus buferį (kaupyklę) ABUF, antruoju - duomenys is registro D siunčiami į VDM ir įrasomi į buferinį registrą (kaupyklę) TMP. ALĮ sudeda kaupyklių ABUF ir TMP turinius ir kitu taktu juos įraso į akumuliatorių. Įvykdzius sią operaciją, VDM lieka laisva ir ją galima panaudoti kitoms operacijoms vykdyti.

42 pav. Magistralės darbo laiko diagramos

Vidine adresų magistrale adresai perduodami į MĮ adresų magistralę. Nuo adresų magistralės pločio m priklauso tiesiogiai valdomos atminties dydis, kuris lygus 2m baitų. Jeigu atmintis yra didesnė negu 2m, ji yra suskaidoma ir valdoma sekcijomis.

Valdymo magistrale perduodami įvairūs valdymo signalai. Jie priklauso nuo mP tipo, tačiau tarp jų visuomet yra atmintinės skaitymo, rasymo, regeneravimo signalai, taip pat signalai informacijai per prievadus (Port) įvesti ir isvesti (42 pav.).

![]() Magistralės darbą

sinchronizuoja taktiniai impulsai. Paveiksle pavaizduotoje diagramoje vienas

magistralės ciklas uztrunka keturis taktus. Adreso signalas yra

ilgiausias, jame telpa kiti valdantieji signalai. Duomenys skaitomi ir

įvedami fiksuotais laiko momentais. Pavyzdziui, pirmojo ciklo pradzioje mP perduoda adreso signalą,

kuris isrenka atmintinės ląstelę. Impulso T2 pradzioje

MEMRD lygis tampa zemas ir jis sujungia atmintinę su duomenų magistrale.

Baigiantis impulsui T4, duomenys perduodami procesoriui.

Magistralės darbą

sinchronizuoja taktiniai impulsai. Paveiksle pavaizduotoje diagramoje vienas

magistralės ciklas uztrunka keturis taktus. Adreso signalas yra

ilgiausias, jame telpa kiti valdantieji signalai. Duomenys skaitomi ir

įvedami fiksuotais laiko momentais. Pavyzdziui, pirmojo ciklo pradzioje mP perduoda adreso signalą,

kuris isrenka atmintinės ląstelę. Impulso T2 pradzioje

MEMRD lygis tampa zemas ir jis sujungia atmintinę su duomenų magistrale.

Baigiantis impulsui T4, duomenys perduodami procesoriui. ![]()

![]() Kai mP magistralės naudoja tik

tris valdančiuosius signalus MEM/IO, RD ir WR, MEM/IO signalo aukstas ir

zemas lygiai nurodo su kuo, atmintine ar prievadu bendraus mP.

Kai mP magistralės naudoja tik

tris valdančiuosius signalus MEM/IO, RD ir WR, MEM/IO signalo aukstas ir

zemas lygiai nurodo su kuo, atmintine ar prievadu bendraus mP.

MĮ gali būti įvairių rūsių atmintinės: operatyvioji (RAM), pastovioji (ROM), pirminė ir antrinė spartinančioji (Cache) ir vidiniai mP registrai. RAM ir ROM yra numeruojamos, o mP registrai zymimi raidėmis. Pirminė spartinančioji atmintinė yra mP mikroschemoje, o antrinė - mP mikroschemoje arba isorėje.

Yra naudojami įvairūs duomenų paieskos (adresavimo) būdai. Kuo įvairesniais būdais mP galima ieskoti duomenų, tuo lanksčiau jį galima programuoti. Pavyzdziui, mP Z80 adresuoti galima net astuoniais būdais:

Naudoti komandą, kuri zino ką ji turi daryti. Tokią komandą sudaro tik operacijos kodas.

Pavyzdziui, komanda NOP nedaro nieko, bet trunka 4 ciklus, o EI tik leidzia pertraukimus.

Adresuoti mP registrą nurodant registrą, kuriame yra reikalingi duomenys. Kai registrų nedaug ji gali tilpti į vieną baitą.

Pavyzdziui: Add Ah, Bh - registro Bh turinį prideda prie registro Ah turinio.

Adresuoti betarpiskai komandoje nurodant duomenį. Sis būdas naudojamas, kai zinoma duomens reiksmė. Komandą sudaro keli baitai. Pirmasis baitas yra operacijos kodas, o kiti - duomenys.

Pavyzdziui: Add Ah, 12H - prie akumuliatoriaus Ah turinio prideda 12H.

Tiesiogiai adresuoti atmintinės ląstelę, kurioje yra reikalingi duomenys. Komanda susideda is operacijos kodo ir adreso. Sį būdą galima naudoti tik kai kurioms komandoms.

Pavyzdziui: JMP 5000H - besąlygiskas suolis į adresą 5000H.

Adresuoti netiesiogiai paimant adresą is specialaus registro. Taip elgiamasi, kai rasant programą duomenys nezinomi ir priklauso nuo operacijos rezultato.

Pavyzdziui: Lea Bx, 5400H - į registrą BX įveda duomenų adresą

Mov Ax, (SI) - į registrą Ax įveda duomenis is registre SI nurodyto adreso.

Prie registre esančio adreso pridedant tam tikrą skaičių - santykinis adresavimas.

Pavyzdziui: JP 0FFCH - grązina per kelis baitus atgal, jei pozymių skiltis P=1. Pozymis P=1 rodo, kad skaičius yra neigiamas.

Prie bazinio adreso pridėti registre SI (DI) esantį indeksą (indeksinis adresavimas). Sis būdas palengvina adreso pakeitimą ir naudojamas dirbant su masyvais.

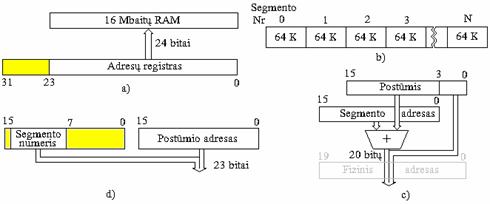

Kai RAM talpa virsija informaciniu zodziu (8 ar 16 bitų) valdomų adresų skaičių, tokiai atmintinei valdyti naudoja du adresavimo būdus: tiesioginį arba segmentinį adresavimą.

Adresuojant tiesioginiu būdu, adresų registras daromas dvigubai ilgesnis uz informacinį zodį, 16 bitų 8 bitų mP ir 32 bitų 16 bitų mP (43 pav., a). Tokiu būdu adresai buvo formuojami, pavyzdziui, firmos "Motorola" 68000 serijos mP.

Adresuojant segmentiniu būdu, visa atmintinė suskirstoma segmentais (43 pav., b), kurių dydį riboja zodzio ilgis. 16 bitų mP segmento dydis yra 64 KB. Segmentai is eilės sunumeruojami. Atmintinę segmentais galima suskirstyti įvairiai. Is segmentų sudarytoje atmintinėje adresas susideda is segmento numerio (segmento adreso) ir postūmio (Offset), kuris nurodo atmintinės ląstelės padėtį segmento pradzios atzvilgiu.

Firmos "Intel" 80x86. serijos mP adresą sudaro segmento (64 KB) adresas ir postūmis (43 pav., c). Abu registrai yra 16 skilčių. Is jų sudaromas 20 skilčių adresas, kuriuo galima valdyti 1 MB atmintinę. Segmento adresą sudaro auksčiausieji 16 (19-3) bitų. Todėl segmentų pradzių adresai turi būti kartotini 16 (nulinio segmento adresas bus 0x16 = 0, pirmojo - 1x16 = 16, antrojo 2x16 = 32 ir t.t iki 4096 segmento adreso). Postūmį sudaro 16 bitų ir jis gali adresuoti 64 KB segmentą. Fizinis adresas apskaičiuojamas segmento adresą padauginus is 16 (10h) ir pridėjus postūmį. Pavyzdziui, kai segmentas lygus 10 ir postūmis lygus 10, fizinis adresas bus 10x16 + 10 = 170.

43 pav. Adresavimas tiesioginiu ir segmentiniu būdu

Firmos "Zilog" mP Z8001 segmento numeriui skirti 7 auksčiausieji segmento registro bitai, todėl segmentų pradzių adresai yra kartotini segmento dydziui, t.y. 64 KB. Adreso registrą čia sudaro 32 bitai ir jis gali valdyti 232 bitų atmintinę.

Komanda vadinamas dvejetainis zodis, kuriuo mP-iui nurodo kokius atlikti veiksmus. Komandą dekoduoja dekoderis, o vykdo valdymo schema.

Kadangi mP yra sinchroninis įtaisas, jo būsenos gali kisti tik fiksuotais laiko momentais. Juos nustato trys laiko intervalai: taktinio daznio periodas (ciklas), mP (magistralės) ciklas ir komandos ciklas. Komandos ciklą gali sudaryti keli mP ciklai, o mP ciklą keli taktai.

44 pav. Komandos sandara

![]() Komanda (44 pav.) susideda is operacijos

kodo ir operando (adreso arba duomenų). Operacijos kodas mP nurodo ką daryti, o

adresas - kur yra duomenys. Jie gali būti mP registre, MĮ vidinėje

atmintyje arba isoriniame įrenginyje. Kelių baitų komandose

pirmasis baitas visuomet yra operacijos kodas. Kai duomenys (pvz., adresas)

uzima du baitus, vienas jų atitinka zemiausiąją (LSB - Least Significant Byte), o kitas auksčiausiąją (MSB - Most Significant Byte) dviejų

baitų skaičiaus skiltį. Pavyzdziui, skaičiaus C8E5h auksčiausioji skiltis bus C8, o zemiausioji E5. Raidė h rodo, kad skaičius parasytas

sesioliktainėje sistemoje. mP Z80 ir Intel 80x86 pirmas adreso baitas

atitinka zemiausiąją skiltį, o antras -

auksčiausiąją skiltį. Kituose mP gali būti atvirksčiai.

Komanda (44 pav.) susideda is operacijos

kodo ir operando (adreso arba duomenų). Operacijos kodas mP nurodo ką daryti, o

adresas - kur yra duomenys. Jie gali būti mP registre, MĮ vidinėje

atmintyje arba isoriniame įrenginyje. Kelių baitų komandose

pirmasis baitas visuomet yra operacijos kodas. Kai duomenys (pvz., adresas)

uzima du baitus, vienas jų atitinka zemiausiąją (LSB - Least Significant Byte), o kitas auksčiausiąją (MSB - Most Significant Byte) dviejų

baitų skaičiaus skiltį. Pavyzdziui, skaičiaus C8E5h auksčiausioji skiltis bus C8, o zemiausioji E5. Raidė h rodo, kad skaičius parasytas

sesioliktainėje sistemoje. mP Z80 ir Intel 80x86 pirmas adreso baitas

atitinka zemiausiąją skiltį, o antras -

auksčiausiąją skiltį. Kituose mP gali būti atvirksčiai.

mP komandos pagal paskirtį yra suskirstytos į tokias 5 grupes:

Komandos duomenims tarp registrų arba tarp registro ir atmintinės persiųsti.

Aritmetinių operacijų (sudėties, atimties, kodo keitimo vienetu) komandos.

Loginių operacijų, perstūmimų, rotacijų komandos.

Kreipimosi į paprogrames, testų, operacijų su steku komandos.

Pertraukimų, informacijos įvedimo ir isvedimo operacijų bei kitos komandos.

Programuojant komanda (operacija) uzrasoma masininiu kodu arba asembleryje anglisko zodzio santrumpa. Pavyzdziui, mP Z80 ir 8080 persiuntimo komandos "registro B turinį perkelti į registrą A" sesioliktainis kodas yra 78, o santrumpos LD (Load) ir MOV (Move). Si komanda mP Z80 asembleryje būtų uzrasoma taip LD A,B, o mP 8080 - MOV A,B.

Tų pačių komandų kodai abiem mP gali būti tie patys, o santrumpos gali skirtis. Pavyzdziui, komandos "registro L turinį pridėti prie akumuliatoriaus (A) turinio" masininis kodas abiem mP yra 85, mP Z80 asembleryje ji uzrasoma ADD A,L, o mP 8080 - ADD L.

Asemblerį daug lengviau įsiminti, negu komandų kodus, todėl mP programos rasomos asembleriu. 3 lentelėje pateikta mP 8080 asembleriu parasyta programa su paaiskinimais, kuri duomenis is prievado, kurio adresas 01, perraso į atmintinę, pradedant adresu 0010h. Programos pradzia atmintinėje yra adresu 0000. Adresai ir duomenys dazniausiai rasomi sesioliktainiame kode.

|

Atmintinės adresas |

Komanda |

Paaiskinimai |

|

LXI H 0010 |

Į registrų H,L porą įraso duomenų pradzios adresą 0010 |

|

|

Zemiausioji skiltis |

||

|

Auksčiausioji skiltis |

||

|

|

IN 01 |

Is prievado 01 į akumuliatorių įraso duomenų baitą |

|

Prievadas |

||

|

MOV M,A |

Akumuliatoriaus turinį įraso į atmintinės ląstelę, kurios adresas, yra H,L registruose |

|

|

INX H |

Prie registrų poros H,L prideda 1 (padidina adresą) |

|

|

JMP 0300 |

Programa persoka į adresą 0003 kitam baitui įvesti |

|

|

Zemiausioji skiltis |

||

|

Auksčiausioji skiltis |

Programą sudaro penkios komandos ir ji uzima 10 atmintinės ląstelių (baitų). Pirmoji programos komanda atmintinėje uzima tris, antroji du, trečioji ir ketvirtoji po vieną, o penktoji tris baitus. Joje yra begalinis ciklas, nes nenurodyta sąlyga jam pabaigti.

Pirmoji komanda adresuoja betarpiskai nurodydama duomenis. Antroji - adresuoja tiesiogiai nurodydama prievadą, is kurio reikia paimti duomenis. Trečioji - netiesiogiai nurodo adresą per registrą. Ketvirtoji - tiesiog adresuoja mP registrą. Penktoji komanda - tiesiogiai nurodydama komandos adresą.

Pertraukimai yra specifinės komandos naudojamos specializuotoms paprogramėms vykdyti, pavyzdziui, MĮ apsikeisti informacija su isoriniu įrenginiu. mP atlikdamas bet kurią komandą tikrina ar nėra pertraukimo. Jį radęs, mP nutraukia duomenų apdorojimą, registro PC turinį persiunčia į steką, o į PC įraso paprogramės pradzios adresą. Steke issaugomi tarpiniai rezultatai ir programos nutraukimo vieta (adresas nuo kurio programa bus tęsiama). PC įrasytu adresu randamas ir paleidziama pertraukimo paprogramė, kuri, pavyzdziui, is prievado įveda duomenis arba per prievad juos isveda. Įvykdęs pertraukimo paprogramę, mP pasiima steke įrasytus duomenis ir tęsia programą.

mP nuosekliai skaito atmintinėje esančias komandas. Pagrindiniai mP veiksmai yra :

komandos nuskaitymas,

komandos vykdymas.

45 pav. Veikimo spartinimas sugretinant komandos isrinkimą ir operacijos vykdymą mP

Vykdydamas komandą mP skaito, apdoroja ir įraso duomenis. Komandos skaitymas vadinamas komandos isrinkimu. Komandos ciklą sudaro komandos isrinkimas ir jos vykdymas. Taktų skaičius reikalingas komandai įvykdyti yra nurodomas mP techninėje dokumentacijoje. Komandos cikle (45 pav., a) pasitaiko laikotarpiai (Pauzė), kai magistralė nenaudojama. Priklausomai nuo informacijos apdorojimo mP trukmės pauzė gali trukti nuo vieno iki kelių desimčių taktų. Vidutinė komandos vykdymo trukmė apskaičiuojama taip:

![]() ,

,

čia TT - takto trukmė, n - mP komandų skaičius, fk - k-osios komandos vykdymo daznis, mk - k-osios komandos taktų skaičius.

mP darbo greičiui padidinti galima isnaudoti pakankamos trukmės pauzes vienos ar net kelių nuoseklių komandų isrinkimui ir įrasymui į vidinius registrus (45 pav., b). Tačiau, kai pasikeičia komandų vykdymo eiliskumas (pvz., iskviečiama paprogramė) įrasytųjų komandų nebegalima panaudoti.

2. Komandų isrinkimas uzima gana daug laiko. Sumazinti isrinkimų skaičių ir tuo pačiu paspartinti mP veikimą galima naudojant sudėtingesnes komandas (46 pav.).

46 pav. Veikimo spartinimas naudojant sudėtingą komandą:

a) - kiekvieną mP registrą valdo atskira komanda; b) - visus mP registrus valdo viena komanda

. Veikimo sparta didėja informaciją apdorojant konvejeriniu būdu (Pipelined), kai ilgai trunkanti operacija yra suskaidoma į trumpesnes ir jos atliekamos nuosekliai sujungtuose įtaisuose, viena paskui kitą. Kad operacija bus atlikta sparčiau, nesunku suvokti įsivaizduojant, pavyzdziui, automobilio surinkimą. Jeigu visą automobilį tektų surinkti vienoje darbo vietoje, tai uztruktų ne vieną valandą. Jį surenkant ant konvejerio, kuriame yra 10 darbo vietų jo surinkimas bus suskaidytas į 10 vienodos trukmės viena po kitos atliekamų operacijų, tai automobilis bus surinktas mazdaug desimt kartų greičiau.

47 pav. Instrukcijos apdorojimas konvejeriniu būdu mP 486 DX2

mP konvejeriniu būdu yra apdorojamos instrukcijos, pavyzdziui, mP 486 programos instrukcija yra apdorojama penkiais ciklais: ji yra skaitoma, per du ciklus dekoduojama, vykdoma ir įrasoma (47 pav.). Athlon procesoriaus konvejerį sudaro 12, o Pentiun 4 net 22 ciklai. Trumpinant ciklus (ilginant konvejerį), galima padidinti procesoriaus darbo daznį (Pentium 4), bet apsirikus ilgiau reikia daugiau laiko konvejeriui isvalyti (mazėja darbo sparta).

mP konstrukcija, korpuso forma, kontaktų skaičius ir jų isdėstymas priklauso nuo jo sudėtingumo. 8 bitų mP buvo pailgo stačiakampio formos ir turėjo 40 kontaktų (48 pav., a). 16 bitų mP kontaktų skaičius nevienodas (48 pav. b). mP 8086 jų turi daug maziau uz MC38000 ir 80286, nes 8086 mikroprocesoriuje tie patys kontaktai naudojami perduoti zemiausiam adresų baitui ir duomenims. Be to mP 80286 korpusas yra kvadratinis ir kontaktai isdėstyti dviem eilėmis. Tokia forma ir kontaktų isdėstymas buvo pradėti naudoti, kai buvo įsisavinta daugiasluoksnių ploksčių gamyba ir yra būdingi siuolaikiniams sudėtingiems mP. Pavyzdziui, mP i386DX turėjo 132, o i486DX - 168 kontaktus isdėstytus trimis eilėmis. Kvadratinės formos yra ir mP Pentium ir kiti procesoriai. Pentium II buvo arytas is kelių mikroschemų sumontuotų plokstėje, kurios gnybtai (liezuvėliai) yra isdėstyti eilėmis abiejose plokstelės pusėse.

48 pav. Kai kurie 8 ir 16 bitų mP

Isvadų skaičiui sumazinti ir mikroschemai atpiginti, kai kada duomenis ir adresus perduoda tais pačiais kontaktais (pvz., mP 8086, 8088, Z8001) arba isorinę duomenų magistralę daro siauresnę uz vidinę (pvz., 8088, i386SX).

|

|

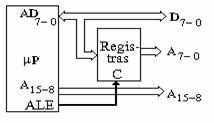

Nesugretintos magistralės pirmojo takto (49 pav.) metu duomenų magistralė nenaudojama. Sugretinus adresų ir duomenų magistrales, sio takto metu duomenų magistrale perduodamas adresas. 49 paveikslėlyje parodyta 8 bitų mP magistralės laiko diagrama, kai duomenų magistrale perduodamas adreso LSB baitas.

49 pav. Sugretintų adresų ir duomenų magistralių laiko diagrama

Pirmojo takto T1 metu bendra

magistrale AD7 - AD0 perduodamas zemiausiasis adreso

baitas. Jį įsimena specialus registras (50 pav.), kurį

atidaro signalo ALE frontas. Registro isvestyse adresas laikomas tol, kol

signalo ALE lygis aukstas. Taip perduodamas zemiausiasis (LSB) adreso

baitas. 50 paveikslėlyje parodyta sugretintų adresų ir

duomenų magistralių sandara.

50 pav.

![]()

![]() mP valdymo signalai priklauso nuo mP tipo, tačiau pagrindiniai

yra būdingi visiems mP. Pavyzdziui, mP Z80 valdymo signalai yra tokie:

INT - sąlyginis pertraukimas (Interruption); NMI - besąlyginis pertraukimas; HALT - mP

sustabdymas; MREQ - operacijos su

atmintine iskvietimas; IORQ -

įvesties (isvesties) iskvietimas; RD

- atmintinės skaitymas; WR -

rasymas į atmintinę; BUSAK

- leidimas kreiptis tiesiog į atmintinę; WAIT - pauzė; BUSRQ

- tiesioginio kreipimosi į atmintinę reikalavimas; RESET - mP grązinimas į

pradinę būseną; MT -

ciklo pradzios signalas; RFSH -

dinaminės atmintinės regeneravimo signalas.

mP valdymo signalai priklauso nuo mP tipo, tačiau pagrindiniai

yra būdingi visiems mP. Pavyzdziui, mP Z80 valdymo signalai yra tokie:

INT - sąlyginis pertraukimas (Interruption); NMI - besąlyginis pertraukimas; HALT - mP

sustabdymas; MREQ - operacijos su

atmintine iskvietimas; IORQ -

įvesties (isvesties) iskvietimas; RD

- atmintinės skaitymas; WR -

rasymas į atmintinę; BUSAK

- leidimas kreiptis tiesiog į atmintinę; WAIT - pauzė; BUSRQ

- tiesioginio kreipimosi į atmintinę reikalavimas; RESET - mP grązinimas į

pradinę būseną; MT -

ciklo pradzios signalas; RFSH -

dinaminės atmintinės regeneravimo signalas.

Kiekvienas MĮ turi didesnės ar mazesnės talpos atmintinę (1 pav.). MĮ atmintinėje saugomos programos, pradiniai ir tarpiniai duomenys, o taip pat informacijos apdorojimo rezultatai. MĮ vidinės atmintinės yra puslaidininkinės. Atmintinės tipas parenkamas priklausomai nuo jos paskirties.

Pagal funkciją atmintinės skirstomos į:

Operatyviąją atmintinę (RAM). Į ją informaciją galima įrasyti ir is jos skaityti realiu laiku.

Pastoviąją atmintinę (ROM). Joje esančią informaciją galima skaityti realiu laiku, o ją įrasyti galima tik vieną kartą arba jai perrasyti sugaistama daug laiko. Informacija atmintinėje islieka ir isjungus maitinimą.

Operatyvioji atmintinė skirstoma į:

- Statinę atmintinę (SRAM - Static RAM), kuri saugo informaciją tol, kol valdymo signalu ji bus pakeista.

- Dinaminę atmintinę (DRAM - Dinamic RAM), kurioje esančią informaciją visą laiką reikia regeneruoti.

Pastovioji atmintinė skirstoma į:

- Neprogramuojamą atmintinę, į kurią programa įrasoma gamybos metu sudarant tam tikrą mikroschemos struktūrą.

- Programuojamą atmintinę (PROM - Programmable ROM, EPROM - Electrical PROM, EEPROM - Electrical Erasable PROM), į kurią galima įrasyti programą ar duomenis. Informacija į PROM tipo atmintinę įrasoma stipria elektros srove nudeginant joje esančius sujungimus, todėl į ją informaciją įrasyti galima tik vieną kartą. Į EPROM tipo atmintinę informacija įrasoma įkraunant krūvius, kurie islieka ilgą laiką (keletą metų). Informacija istrinama apsvietus mikroschemą ultarvioletiniais spinduliais per specialų langelį. Į tokią atmintinę informaciją galima įrasyti daug kartų. Į EEPROM atmintinę informacija įrasoma ir is jos trinama elektriniu signalu po baitą, t.y. informaciją galima keisti dalimis.

- "Flash" tipo atmintinę, į kurią informaciją normaliu signalu galima sparčiai is jos skaityti ir palyginti sparčiai įrasyti. Joje įrasyta informacija neisnyksta isjungus maitinimą. Todėl ji dazniausiai atlieka pastoviosios atmintinės funkcijas ir nesiojamose įtaisuose pradedama naudoti vietoje tradicinių informacijos kaupiklių. Jos yra kompaktiskos, bet palyginti brangios. Ateityje "Flash" tipo atmintinės gali pakeisti isorinius kaupiklius. "Flash" tipo atmintinė yra viena is EEPROM modifikacijų.

- Isorinius informacijos kaupiklius (pvz., diskinį, disketinį, CD-ROM).

Operatyvioji atmintinė yra skirta įkrautoms programoms, tarpiniams informacijos apdorojimo bei galutiniams rezultatams saugoti. Isjungus maitinimą, informacija is RAM isnyksta. Statinės atmintinės (SRAM) yra sudarytos is trigerių, todėl jos informaciją saugo tol, kol valdymo signalas pakeičia trigerio būseną. Tokios atmintinės yra spartesnės, paprasčiau valdomos, bet brangesnės ir ne tokios kompaktiskos kaip DRAM. Dinaminės atmintinės sudarytos is elementų, kurie tik trumpam įsimena informaciją (pvz., krūvį MOP tranzistoriaus uztūros parazitinėje talpoje). Tokios atmintinės yra pigesnės, kompaktiskesnės ir vartoja maziau energijos. Todėl jos labai paplito, nepaisant sudėtingesnio valdymo ir lėtesnio veikimo. Pastovioji atmintinė naudojama MĮ funkcionavimo valdymo programai ir nekintantiems duomenims saugoti.

Bendrieji parametrai:

Veikimo sparta. Ji priklauso nuo dviejų kreipimosi laikų (Access Time) tRAC (kreipimosi trukmė pasirodzius signalui RAS), tCAC (kreipimosi trukmė pasirodzius signalui CAS) ir skaitymo ciklo trukmės tRC. (Read Cycle Time).

SRAM atmintinių minimalus kreipimosi laikas tRAC yra kelios ns, DRAM - 30 ns, PROM - 100 ns. SRAM ir PROM tipo atmintinių kreipimosi laikas gali būti lygus takto ilgiui, DRAM jis turi būti mazesnis.

|

|

![]()

51 pav. Firmos "Intel" RAM atmintinių mikroschemų pavyzdziai

Atmintinės talpa (Memory Size). Ji matuojama bitais (baitais), Kbitais (KB) ir Mbitais (MB). Pavyzdziui, mikroschemos 21256 ir 21464 (51 pav.) yra 256144 bitų talpos RAM, o mikroschemos 21010 talpa yra 1048576 bitai. Mikroschemų rinkinio iSM001DR09 sudaryto is 9 1048576 bito talpos mikroschemų talpa yra 1048576 baitų, nes 9-oji mikroschema yra skirta lygiskumo kontrolei.

Atmintinės organizacija. Nuo jos priklauso talpinamų zodzių skaičius ir zodzio ilgis. Ji koduojama zodzių skaičiaus ir zodzio ilgio sandauga. Pavyzdziui (51 pav.), mikroschema 21256 talpina 256144 vieno bito ilgio zodzius (256144 x 1). Ji turi po vieną kontaktą duomenims įvesti ir isvesti. Tos pačios talpos mikroschema 21464 talpina 65536 keturių bitų ilgio zodzius (65536 x 4). Ji turi keturis sugretintus kontaktus duomenims įvesti ir isvesti. Mikroschema 21010 talpinanti 1048576 bitus turi po vieną kontaktą duomenims įvesti ir isvesti, todėl ji talpina 1048576 vieno bito zodzius. ISM001DR09 yra 1M x 9 (1048576 x 9). Ji talpina 1048576 devynių bitų zodzius.

Suvartojamoji galia (Power Consumption). Dinaminės atmintinės yra gerokai ekonomiskesnės uz statines.

Maitinimo įtampos. 51 paveikslėlyje parodytų mikroschemų maitinimo įtampa VCC = +5V.

Konstrukcija. Mazos talpos atmintinės yra DIP (Dual-In-Line) korpusuose, didesnės SIMM (Single In-Line-Memory Module) mikroschemų rinkiniuose, kai vienoje plokstelėje yra sumontuotos kelios mikroschemos (51 pav.). Jos yra 8(9) bitų (256 KB, 1, 4, 16 MB talpos) ir 32(36) bitų (1, 4, 16, 32 MB talpos). Dar didesnės talpos atmintinėms naudojami DIMM (Dual In Line Memory Module) rinkiniai, kurie turi atskirtus 168 kontaktus abiejose plokstelės pusėse. DIMM modulių talpa yra 64, 128, 256 ir 512 MB.

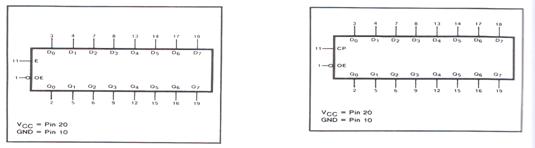

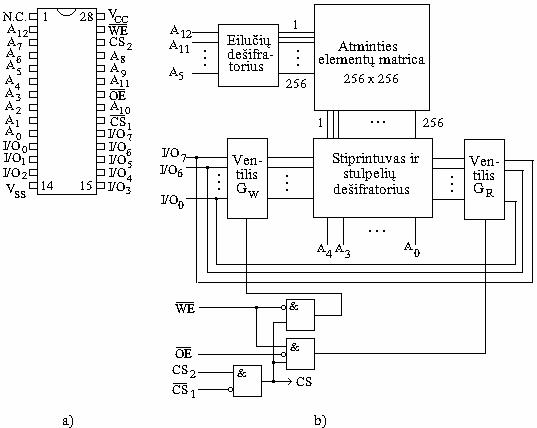

Statinės 8 Kbitų x 8 atmintinės mikroschemos struktūra parodyta 52 paveiksle.

I/O įvesties ir isvesties

duomenys WE įrasymo leidimas CS1 CS2 mikroschemos isrinkimas OE skaitymo leidimas![]()

![]()

![]()

52 pav. 64 Kbitų statinės atmintinės mikroschemos kontaktų isdėstymas (a) ir struktūra (b)

![]() Atmintinėje telpa 8192 astuonių bitų zodziai. Kiekvienas

zodis įrasomas ir skaitomas lygiagrečiai per astuonis kontaktus (I/O0

- I/O7). Joje yra 13 kontaktų (213 = 8192) adresams

(A0 - A12). Atmintinė valdoma 4 signalais (WE, OE,

CS1, CS2). Atmintinės elementai (trigeriai) sudaro

256 x 256 matricą. Eilutė isrenkama dekoduojant 8 vyriausiuosius

(MSB) adreso bitus (A5 - A12), o stulpelis - desifruojant

jauniausiuosius (LSB) 5 adreso bitus (A0 - A4).

Desifruojamos 256 eilutės ir 32 stulpeliai, kurių kiekviename yra 8

bitų zodis. Kai atmintinę sudaro kelios mikroschemos, į

kurią jų informaciją rasyti ar is kurios ją skaityti,

nurodo signalai CS2 ir CS1. Nagrinėjama mikroschema

yra isrenkama, kai CS2 =1, C1 = 0. Informacija įrasoma,

kai WE = 0, o skaitoma, kai OE = 0. Jeigu jie pasirodo vienu metu WE uzdraudzia

OE. 53 pav. parodytos nagrinėjamos mikroschemos laiko diagramos.

Atmintinėje telpa 8192 astuonių bitų zodziai. Kiekvienas

zodis įrasomas ir skaitomas lygiagrečiai per astuonis kontaktus (I/O0

- I/O7). Joje yra 13 kontaktų (213 = 8192) adresams

(A0 - A12). Atmintinė valdoma 4 signalais (WE, OE,

CS1, CS2). Atmintinės elementai (trigeriai) sudaro

256 x 256 matricą. Eilutė isrenkama dekoduojant 8 vyriausiuosius

(MSB) adreso bitus (A5 - A12), o stulpelis - desifruojant

jauniausiuosius (LSB) 5 adreso bitus (A0 - A4).

Desifruojamos 256 eilutės ir 32 stulpeliai, kurių kiekviename yra 8

bitų zodis. Kai atmintinę sudaro kelios mikroschemos, į

kurią jų informaciją rasyti ar is kurios ją skaityti,

nurodo signalai CS2 ir CS1. Nagrinėjama mikroschema

yra isrenkama, kai CS2 =1, C1 = 0. Informacija įrasoma,

kai WE = 0, o skaitoma, kai OE = 0. Jeigu jie pasirodo vienu metu WE uzdraudzia

OE. 53 pav. parodytos nagrinėjamos mikroschemos laiko diagramos.

Gw

atviras

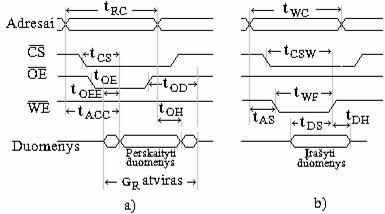

53 pav. Statinės RAM skaitymo ir rasymo ciklų diagramos

Skaitant duomenis pirmiausia randamas adresas, po to isrenkama mikroschema ir tik tada siunčiamas signalas, kuris leidzia skaityti duomenis. Į duomenų magistralę (I/O) duomenys is atmintinės isvedami per ventilį GR.

Duomenų skaitymo ciklo diagramoje (53 pav., a) pazymėti tokie laikotarpiai:

tACC - duomenų isrinkimo laikas. Jį sudaro laikotarpis nuo adreso atsiradimo iki duomenų isvedimo pradzios;

tCS - laikotarpis nuo kristalo isrinkimo (Cristal Select) iki duomenų isvedimo pradzios;

tOE - laikotarpis nuo momento, kai signalas OE (Output Enable) tampa lygus 0, iki duomenų isvedimo pradzios;

tOEE - laikotarpis nuo momento, kai signalas OE (Output Enable) tampa lygus 0, iki atsidaro ventilis GR;

tOD - laikotarpis nuo momento, kai signalas OE (Output Enable) tampa lygus vienetui iki uzsidaro ventilis GR (Output Disabled);

tOH - laikotarpis, kurį adresui pasikeitus duomenys islaikomi nepakitę (Output Hold Back);

tRC - duomenų skaitymo ciklo trukmė (Read Cycle).

Duomenis įrasomi panasiai kaip ir skaitomi, tik, vietoje signalo leidziančio skaityti duomenis, atsiunčiamas signalas leidziantis rasyti duomenis. Duomenys į atmintinę is duomenų magistralės (I/O) įvedami per ventilį GW .

Duomenų įrasymo ciklo diagramoje (53 pav., b) pazymėti tokie laikotarpiai:

tCSW - laikotarpis nuo mikroschemos isrinkimo iki duomenų įrasymo (Crystal Select Write);

tWP - laikotarpis, kada signalas WE yra lygus nuliui;

tOS - laikotarpis duomenimis įrasyti;

tAS - laikotarpis nuo adreso suradimo iki tol, kol WE pasidaro lygus nuliui;

tDH - laikotarpis kurį, po to kai WE pasidaro lygus vienetui, įrasomieji duomenys nekinta (Data Hold Back);

tWC - duomenų įrasymo ciklas (Write Cycle).

Statinių atmintinių valdymas nesudėtingas, jas galima valdyti mikroprocesoriaus signalais. 54 paveiksle parodyta 64K x 16 bitų atmintinės sudarytos is 8K x 8 bitų mikroschemų struktūra.

Atmintinę sudaro 8 mikroschemų poros. Virsutinėse mikroschemose talpinamas auksčiausiasis duomenų baitas, o apatinėse - zemiausiasis. Poras isrenka trys vyriausieji adreso bitai, nes kiekvienoje poroje telpa 8K sesiolikos bitų zodzių. Zodzius isrenka pirmieji trylika adreso bitai. Auksčiausiąjį ir zemiausiąjį baitus isrenka atskiri signalai.

![]() Is daugelio mikroschemų sudaryta

atmintinė gali būti suskirstoma moduliais, kurie isrenkami panasiai,

kaip mikroschemų poros.

Is daugelio mikroschemų sudaryta

atmintinė gali būti suskirstoma moduliais, kurie isrenkami panasiai,

kaip mikroschemų poros.

Reikalui esant tarp mP ir atmintinės jungiami magistralės signalų formuotuvai.

Duomenys įvedami (D) ir isvedami (Q) atskirai. Adresui įvesti yra 9 kontaktai (A0 - A8). Adresą sudaro 18 bitų (218 = 262144). Pirmiausia siunčiami auksčiausieji bitai. Registrai įsimena atmintinės eilutę ir stulpelį. Eilutės adresą skaito signalas RAS (Row Adress Strob), o stulpelio - CAS (Column Adress Strob). Signalas WE (Write Enable) valdo rasymą į atmintinę. Eilučių desifratorius isrenka eilutę, stulpelių desifratorius - stulpelį. Duomenys įsimenami įkraunant talpas. Naudojami du duomenų įrasymo būdai:

pav. 64 x 16 bitų statinės atmintinės struktūra

Atmintinės

elementų matrica

- isankstinis

duomenų įrasymas, kai is įvesties D paimti duomenys

įrasomi per stulpelių desifratoriaus isrinktą skaitymo

stiprintuvą. Duomenų isvestis Q yra atjungta;

- duomenų skaitymas ir įrasymas, kai ląstelėje esantys duomenys perskaitomi ir perduodami į isvestį Q, o po to įrasomi nauji duomenys is įvesties D.

Atmintinėje duomenys regeneruojami juos skaitant, rasant arba specialiai kas kelios ms, per eilučių skaitiklio (57 pav.) signalais valdomus stulpelių desifratorių ir skaitymo stiprintuvą. Kiekvieną mikroschemą galima regeneruoti nepriklausomai nuo kitų.

56 paveiksle parodytos dinaminės atmintinės skaitymo ir rasymo į ją laiko diagramos.

55 pav. Dinaminės 256 Kbitų atmintinės mikroschemos sandara

![]()

Pirmiausia paduodamas

eilutės isrinkimo signalas

RAS (Row Adress Selection). Po to -

stulpelio isrinkimo signalas CAS (Column

...). Skaitymo ciklo metu signalas WE = 1. Intervalai tRAS ir tRF

atitinka minimalų laiką, kurį signalo RAS reiksmė yra lygi

0 arba 1. tRAS + tRF = tRC yra minimali

skaitymo ciklo trukmė. Rasymo ciklo trukmė yra tWC.

Visų laiko diagramose nurodytų laikotarpių minimalios

reiksmės yra duodamos mikroschemos dokumentacijoje. Is laiko diagramų

matyti, kad dinaminių atmintinių valdymas yra sudėtingas.

Joms valdyti naudojami specialūs valdikliai, kurie laike suderina

valdymo ir regeneravimo signalus. Tokio valdiklio struktūrinė

schemos pavyzdys parodytas 57 paveiksle.

Pirmiausia paduodamas

eilutės isrinkimo signalas

RAS (Row Adress Selection). Po to -

stulpelio isrinkimo signalas CAS (Column

...). Skaitymo ciklo metu signalas WE = 1. Intervalai tRAS ir tRF

atitinka minimalų laiką, kurį signalo RAS reiksmė yra lygi

0 arba 1. tRAS + tRF = tRC yra minimali

skaitymo ciklo trukmė. Rasymo ciklo trukmė yra tWC.

Visų laiko diagramose nurodytų laikotarpių minimalios

reiksmės yra duodamos mikroschemos dokumentacijoje. Is laiko diagramų

matyti, kad dinaminių atmintinių valdymas yra sudėtingas.

Joms valdyti naudojami specialūs valdikliai, kurie laike suderina

valdymo ir regeneravimo signalus. Tokio valdiklio struktūrinė

schemos pavyzdys parodytas 57 paveiksle.

56 pav. Dinaminės atmintinės skaitymo ir rasymo į ją ciklų laiko diagramos

Valdiklis is mP signalų suformuoja signalus atmintinei valdyti ir regeneruoti bei suderina mP ir regeneravimo signalus, kurie yra nepriklausomi vienas nuo kito. Tam skirtas arbitras. Pavyzdziui, jeigu atmintinės skaitymo - rasymo ciklo metu ateina regeneravimo signalas, jis yra sulaikomas iki operacijos pabaigos ir atvirksčiai. Regeneravimo laikrodis nustato regeneravimo periodą. Adreso komutatorius perduoda auksčiausiuosius arba zemiausiuosius adreso bitus is adresų magistralės, arba eilučių adresus atmintinės regeneravimui. Atmintinių darbo patikimumui padidinti kiekvienam atmintinės zodziui yra skirtas papildomas lygiskumo bitas į kurį, pavyzdziui, rasomas nulis, kai vienetų skaičius zodyje lyginis arba vienas, kai jis nelyginis. Skaitant atmintinę lygiskumas tikrinamas. Tai padeda pastebėti klaidą vienoje zodzio skiltyje. Kai kada naudojamos schemos istaisančios 1 ir randančios dvi klaidas.

2.7 pav. Dinaminés atminties valdiklio

struktúriné schema

57 pav. Dinaminės atminties valdiklio struktūrinė schema

Greitoji puslapiuojama (Fast Page Mode - FPM) DRAM

Tokios DRAM veikimas skiriasi nuo paprastos DRAM veikimo tuo, kad kai signalo RAS lygis pasidaro zemas isrenkama eilutė ir po to keičiant tik signalą CAS yra kreipiamasi is eilės į kelis tos pačios eilutės stulpelius. Taip sutaupoma laiko, informacija paimama arba įrasoma per maziau ciklų.

58 pav. Greitosios puslapiuojamos DRAM supaprastintos veikimo diagramos

DRAM su kaupykle isvestyje (Extended Data Output DRAM - EDO DRAM)

EDO DRAM kiekvienoje isvestyje turi kaupyklę (Gate Latch), į kurią įrasyta informacija islieka iki tol kol CAS lygis pasidaro zemas, t.y. stulpelio isrinkimo metu. Dėl to CAS impulsų daznis gali būti didesnis. Tokios atmintinės tinka naudoti MĮ, su sisteminėmis magistralėmis, kurių darbo daznis siekia 66 MHz (skaitymo - rasymo ciklas, 59 pav.).

59 pav. DRAM su kaupykle isvestyje supaprastintos veikimo diagramos

DRAM su registru isvestyje (Burst EDO DRAM - BEDO DRAM)

Jos turi vidinį keturių adresų skaitiklį ir kaupyklę keturiems isvedamiems duomenims. Todėl keturių duomenų sekai nuskaityti pakanka nurodyti tik pirmojo duomens adresą, o duomenis is registro galima pradėti isvesti vėliau ir greičiau. Jos tinka MĮ, kurių magistralė dirba 66 MHz.

Sinchroninės DRAM (SDRAM)