Electronica si Telecomunicatii

Proiect PAC2

~ Tema de proiect nr. 15 ~

Tehnologia CMOS impusa : CMOS_AMIS_050_T49M

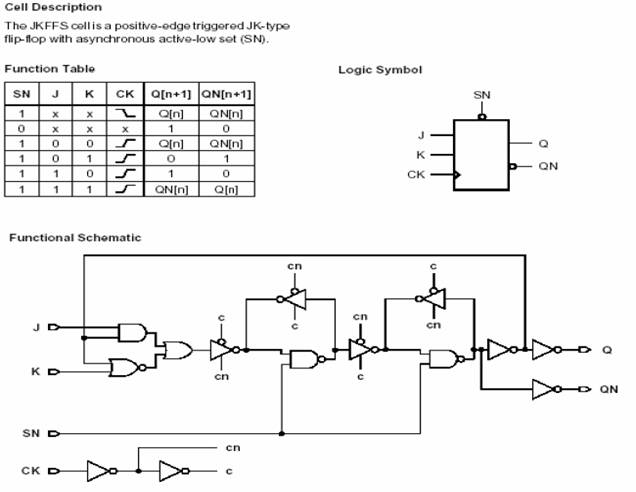

Partea I - Proiectarea si analiza dinamica in Spice a circuitului JKFFS

Sa se dimensioneze tranzistoarele MOS corespunzator tehnologiei date si sa se scrie netlist-ul SPICE al circuitului. (Netlist-ul se va scrie ierarhic folosind subcircuite).

Sa se efectueze analiza tranzitorie a circuitului pentru a pune in evidenta functionarea sa. La fiecare iesire a circuitului se va considera cite o capacitate de sarcina. Valorile pentru tensiunea de alimentare VD 555g68f D 555g68f , timpii de tranzitie TR ai formelor de unda de la intrari si, respectiv, capacitatile de sarcina CL se vor adopta in functie de tehnologia impusa conform tabelului urmator:

|

Tehnologie CMOS |

0.13 μm |

0.18μm |

0.25μm |

0.35μm |

0.50μm |

|

VD 555g68f D 555g68f |

1.2V |

1.8V |

2.5V |

3.3V |

5V |

|

TR |

0.1ns |

0.15ns |

0.2ns |

0.3ns |

0.4n |

|

CL |

0.06pF |

0.07pF |

0.08pF |

0.09pF |

0.1pF |

D 555g68f eterminati prin simulare parametrica si folosind functii tinta in Probe dependenta timpilor de propagare a circuitului (de la intrarea de clock la iesiri) in functie de capacitatea de sarcina (CL), respectiv in functie de timpul de tranzitie (TR) al formei de unda al intrarii de clock. In ambele analize parametrice variatia parametrilor se va face in intervalul (0.5 1.5)* val. adoptata conform tehnologiei. D 555g68f eterminati si notati pe graficele obtinute valorile intarzierilor de propagare corespunzatoare valorilor adoptate pentru CL si TR.

Considerand ca dependenta timpilor de propagare in functie de CL este de forma:

tptotal = tpintrinsec + Kload*CL

determinati pe baza graficelor obtinute valorile pentru tpintrinsec si Kload si completati un tabel de felul urmator (tpintrinsec corespunde valorii CL=0pF):

|

D 555g68f escriere |

tpLH |

tpHL |

||

|

tpLHintrinsec |

Kload |

tpHLintrinsec |

Kload |

|

|

CK → Q | ||||

|

CK → QN | ||||

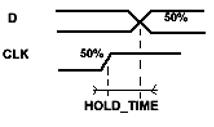

D 555g68f eterminati prin simulare parametrii de constrangere SETUP_TIME, HOLD 555g68f _TIME si durata minima a pulsului MINPW pentru pinii de intrare specificati in tabelul urmator:

|

Pin intrare |

Parametru constrangere |

D 555g68f urata interval [ns] |

|

K |

SETUP_TIME_LH → CK | |

|

SETUP_TIME_HL → CK | ||

|

HOLD 555g68f _TIME_LH → CK | ||

|

HOLD 555g68f _TIME_HL → CK | ||

|

CK |

MINPW_HIGH | |

|

MINPW_LOW |

Pentru simularile efectuate la fiecare din punctele 2, 3 si 4 se vor prezenta schema de test, fisierul SPICE .cir) si formele de unda sau caracteristicile reprezentative pe baza carora s-au determinat parametrii ceruti in tabele.

Mai jos sunt prezentate descrierea, schema bloc si tabelul de functionare al circuitului.

PARTEA II - VHD 555g68f L

A. i) Sa se implementeze in VHD 555g68f L un model comportamental pentru circuitul proiectat si analizat dinamic in Partea I. In cadrul modelului se vor defini si utiliza constante generice pentru parametrii dinamici determinati prin simulare (timpi de propagare clock→iesire, setup_time si hold_time).

ii) Sa se implementeze o entitate de test si sa se simuleze modelul de la punctul i)

B. D 555g68f enumirea circuitului: Circuit de selectie si comanda a unui sistem de doua lifturi

D 555g68f escriere circuit:

Circuitul selecteaza si comanda un sistem cu doua lifturi, A si B intr-o cladire cu 8 nivele (parter+7etaje) in urma unei cereri de chemare.

La fiecare etaj exista un singur buton pentru chemarea unuia din cele doua lifturi. Cand la un anumit etaj s-a apasat butonul de chemare a liftului, circuitul va determina si va selecta liftul situat cel mai aproape de locul chemarii si, totodata, va transmite acestuia sensul si numarul de nivele pe care trebuie sa le parcurga pana la locul chemarii. D 555g68f aca lifturile se afla la aceeasi distanta fata de locul chemarii, atunci va fi selectat liftul A.

Pentru simplitate se va presupune ca intotdeauna cand este apasat un buton de chemare, lifturile stationeaza.

Pentru circuit se vor considera urmatoarele porturi:

|

D 555g68f enumire |

Mod |

Semnificatie |

|

R[0:7] |

intrare |

Semnal pe 8 biti corespunzator butoanelor de la fiecare etaj pentru chemarea unui lift. Exemplu: cand R(5) ia valoarea '1' se considera ca la etajul 5 s-a apasat butonul pentru chemarea unui lift. |

|

PLA[2:0] |

intrare |

Semnal pe 3 biti care indica valoarea in binar a pozitiei (etajului) unde este situat liftul A. Exemplu: daca PLA="010", liftul A este la etajul 2. |

|

PLB[2:0] |

intrare |

Semnal pe 3 biti care indica valoarea in binar a pozitiei liftului B. |

|

SELA |

iesire |

Port pentru selectia liftului A. D 555g68f aca SELA='1', liftul A este selectat pentru a se deplasa la locul chemarii. |

|

SELB |

iesire |

Port pentru selectia liftului B. Similar ca SELA. |

|

SENS |

iesire |

Port care indica sensul in care trebuie sa se deplaseze liftul selectat: '1' - urcare; '0' - coborare. |

|

D 555g68f IST[2:0] |

iesire |

Port care indica in binar numarul de nivele pe care trebuie sa le parcurga liftul selectat pana la locul chemarii. |

Cerinte:

i) Sa se realizeze un model comportamental in VHD 555g68f L a circuitului.

ii) Sa se implementeze un testbench pentru verificarea modelului circuitului. In cadrul simularii se vor aplica tranzitii la intrari astfel incat sa se testeze raspunsul circuitului pentru cateva din situatiile posibile.

Partea I - Proiectarea si analiza dinamica in Spice a circuitului JKFFS

1. D 555g68f imensionarea tranzistoarelor MOS corespunzator tehnologiei date si netlist-ul SPICE al circuitului.

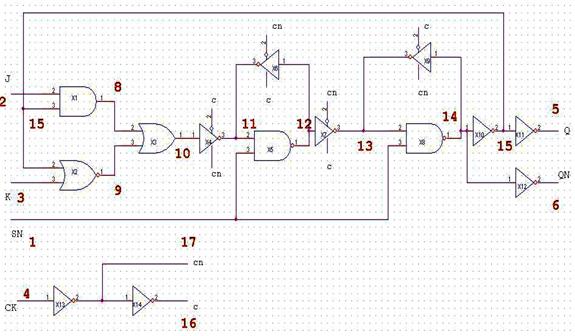

Schema contine urmatoarele porti logice: AND 555g68f 2, NOR2, OR2, NAND 555g68f 2, inversoare simple si inversoare comandate.

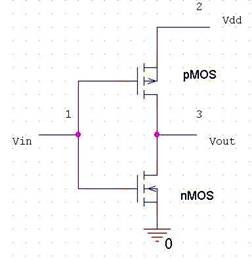

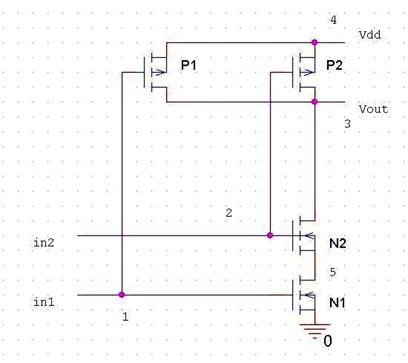

Structura la nivel de tranzistor a portii inversoare :

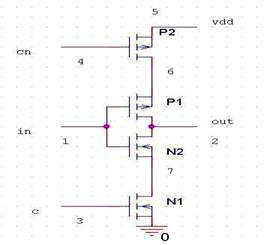

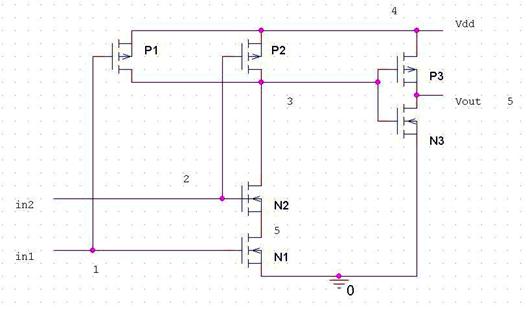

Structura la nivel de tranzistor a portii inversoare comandate:

Pentru dimensionarea tranzistoarelor in cazul portilor inversoare si a portilor inversoare comandate se pleaca de la conditia :

![]()

Rezistenta dinamica este:

![]() ;

; ![]()

Tinand cont ca tensiunile de prag

![]() si

si ![]() sunt relative egale si

sunt relative egale si

![]() , rezulta relatia de

dimensionare care face legatura intre parametrii de proiectare si parametrii de

proces:

, rezulta relatia de

dimensionare care face legatura intre parametrii de proiectare si parametrii de

proces:

![]()

Latimea unui tranzistor cu canal p se considera de 2-3 ori mai mare decat cea a unui tranzistor cu canal n

D 555g68f in datele continute in tehnologia impusa rezulta:

![]()

![]()

Astfel: ![]()

Latimea minima a tranzistoarelor se va adopta la alegere din intervalul (1.5 4)*L :

![]()

![]()

![]() deci

deci ![]() .

.

Implementarea in Spice a inversorului simplu este:

*inversor

* ordinea terminalelor: in out vdd

.subckt INV 1 2 3

* <nod_drena> <nod_poarta> <nod_sursa> <nod_substrat>

MP1 2 1 3 3 CMOSP L=0.5u W=2.59u

MN1 2 1 0 0 CMOSN L=0.5u W=1.25u

.ends

Implementarea in Spice a inversorului comandat este :

*inversor comandat

* ordinea nodurilor: in out c cn vdd

.subckt INVC 1 2 3 4 5

<nod_drena> <nod_poarta> <nod_sursa> <nod_substrat>

MP1 2 1 6 5 CMOSP L=0.5u W=2.59u

MP2 6 4 5 5 CMOSP L=0.5u W=2.59u

MN1 7 3 0 0 CMOSN L=0.5u W=1.25u

MN2 2 1 7 0 CMOSN L=0.5u W=1.25u

.ends

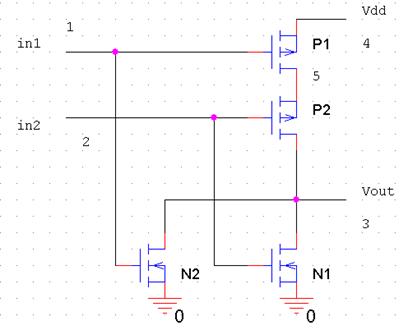

Structura la nivel de tranzistor a portii NAND 555g68f cu doua intrari:

Structura la nivel de tranzistor a portii AND 555g68f cu doua intrari este:

Pentru dimensionarea tranzistoarelor in cazul portilor NAND 555g68f si AND 555g68f se

pleaca de la conditia : ![]() deci pentru poarta cu

doua intrari va fi:

deci pentru poarta cu

doua intrari va fi: ![]() .

.

![]()

D 555g68f eoarece raportul coeficientilor a rezultat ![]() va rezulta:

va rezulta:

![]()

![]()

![]()

Latimea minima a tranzistoarelor se adopta la alegere din intervalul (1.5 4)*L:

![]() de unde rezulta

de unde rezulta ![]() iar

iar ![]() .

.

Implementarea in Spice a subcircuitului pentru poarta NAND 555g68f 2 este:

*poarta NAND 555g68f 2

*ordinea nodurilor: in1 in2 out vdd

.subckt NAND 555g68f 2 1 2 3 4

<nod_drena> <nod_poarta> <nod_sursa> <nod_substrat>

MP1 3 1 4 4 CMOSP L=0.5u W=1.29u

MP2 3 2 4 4 CMOSP L=0.5u W=1.29u

MN1 5 1 0 0 CMOSN L=0.5u W=1.25u

MN2 3 2 5 0 CMOSN L=0.5u W=1.25u

.ends

Implementarea in Spice a subcircuitului pentru poarta AND 555g68f 2 este :

*poarta AND 555g68f 2

* ordinea terminalelor in1 in2 out vdd

.subckt AND 555g68f 2 1 2 3 4

XNAND 555g68f 2 1 2 5 4 NAND 555g68f 2

XINV 5 3 4 INV

.ends

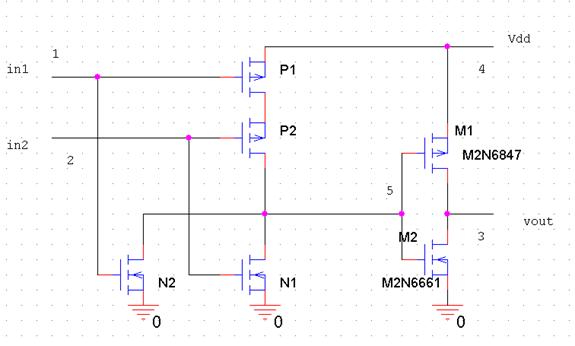

Structura la nivel de tranzistor a portii NOR cu doua intrari:

Structura la nivel de tranzistor a portii OR cu doua intrari:

Pentru dimensionarea tranzistoarelor in cazul portilor NOR si OR se pleaca

de la conditia : ![]() deci pentru poarta cu

doua intrari va fi:

deci pentru poarta cu

doua intrari va fi: ![]() .

.

![]()

D 555g68f eoarece raportul coeficientilor a rezultat ![]() va rezulta:

va rezulta:

![]()

![]()

![]()

Latimea minima a tranzistoarelor se adopta la alegere din intervalul (1.5 4)*L:

![]() de unde rezulta

de unde rezulta ![]() iar

iar ![]() .

.

Implementarea in Spice a subcircuitului pentru poarta NOR2 este:

*poarta NOR cu 2 intrari

*ordinea terminalelor: in1 in2 out Vdd

.subckt NOR2 1 2 3 4

<nod_drena> <nod_poarta> <nod_sursa> <nod_substrat>

MP1 5 1 4 4 CMOSP L=0.5u W=5.17u

MP2 3 2 5 4 CMOSP L=0.5u W=5.17u

MN1 3 1 0 0 CMOSN L=0.5u W=1.25u

MN2 3 2 0 0 CMOSN L=0.5u W=1.25u

.ends

*poarta OR cu 2 intrari

*ordinea terminalelor: in1 in2 out Vdd

<nod_drena> <nod_poarta> <nod_sursa> <nod_substrat>

.subckt OR2 1 2 3 4

XNOR2 1 2 5 4 NOR2

XINV 5 3 4 INV

.ends

Implementarea in Spice pentru subcircuitul JKFFS este:

*subcircuit JKFFS

.inc INV.cir

.inc OR2.cir

.inc NOR2.cir

.inc AND 555g68f 2.cir

.inc NAND 555g68f 2.cir

.inc INVC.cir

*ordinea terminalelor: sn,j,k,ck,q,qn,vdd

.subckt JKFFS 1 2 3 4 5 6 7

X1 2 15 8 7 AND 555g68f 2

X2 15 3 9 7 NOR2

X3 8 9 10 7 OR2

X4 10 11 16 17 7 INVC

X5 11 1 12 7 NAND 555g68f 2

X6 12 11 17 16 7 INVC

X7 12 13 17 16 7 INVC

X8 13 1 14 7 NAND 555g68f 2

X9 14 13 16 17 7 INVC

X10 14 15 7 INV

X11 15 5 7 INV

X12 14 6 7 INV

X13 4 16 7 INV

X14 16 17 7 INV

.ends2.

Analiza tranzitorie:

*Analiza circuitului JKFFS

.inc JKFFS.cir

XJKFFS 1 2 3 4 5 6 7 JKFFS

VCK 4 0 pulse(0 3ns 3ns 6ns)

VSN 1 0 pulse(0 0 40ns 80ns)

VJ 2 0 pulse(0 0.5ns 12ns 24ns)

VK 3 0 pulse(0 0.5ns 16ns 32ns)

Vdd 7 0

CQ 5 0

CQN 6 0

.param CL 0.1p

.param TR 0.4n

.param Vdd 5

.inc D 555g68f :scoalapacproiectCMOS_AMIS_050_T49M.TXT

.TRAN 0.1ns 60ns 0 0.1ns

.PROBE

.END 555g68f

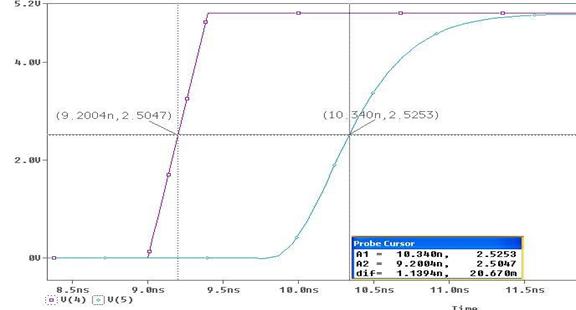

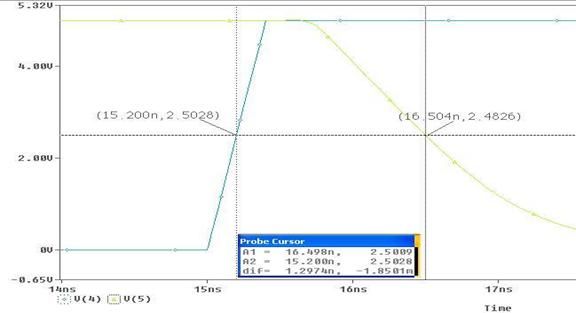

Rezultatele analizei tranzitorii:

Functiile timpilor de propagare sunt urmatoarele:

tpLH(1,2)=x2-x1

tpHL(1,2)=x2-x1

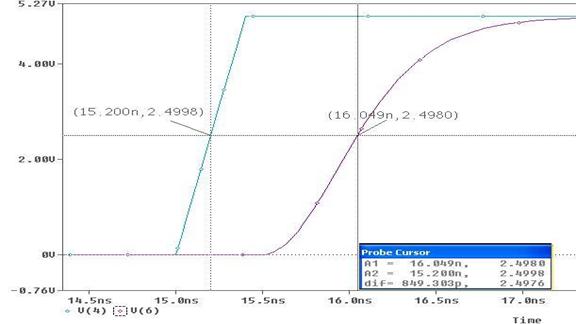

D 555g68f ependenta timpilor de propagare tpHL si tpLH, de la intrarea de CK la iesirea Q in functie de capacitatea de sarcina CL :

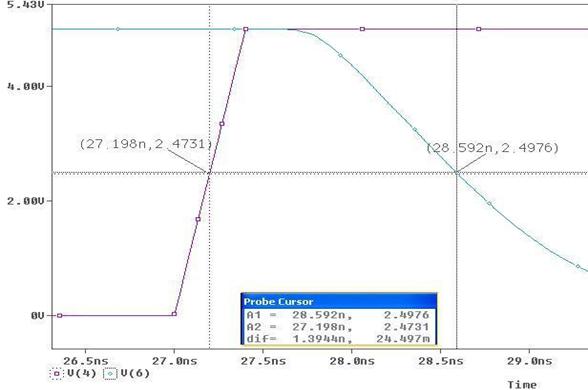

D 555g68f ependenta timpilor de propagare tpHL si tpLH, de la intrarea de CK la iesirea QN in functie de capacitatea de sarcina CL:

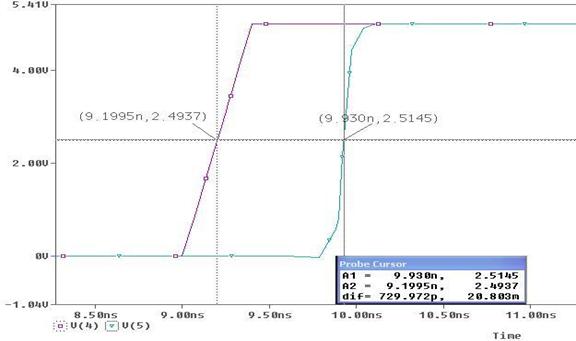

D 555g68f ependenta timpilor de propagare tpHL si tpLH, de la intrarea de CK la iesirea Q in functie de timpul de tranzitie TR:

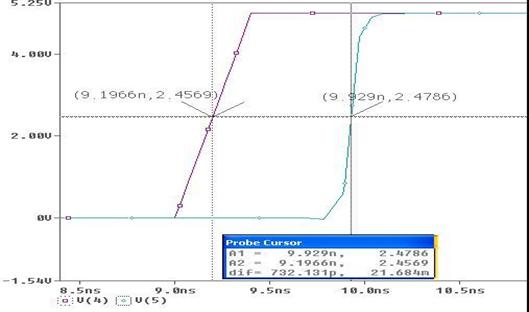

D 555g68f ependenta timpilor de propagare tpHL si tpLH, de la intrarea de CK la iesirea QN in functie de timpul de tranzitie TR:

D 555g68f eterminarea timpilor de propagare:

CL=0,1pF

![]()

![]()

![]()

![]()

CL=0pF

![]()

![]()

![]()

![]()

D 555g68f ependenta timpilor de propagare in functie de CL este de forma:

![]()

D 555g68f in datele experimentale rezulta urmatorul tabel:

|

D 555g68f escriere |

tpLH |

tpHL |

||

|

tpLHintrinsec |

Kload |

tpHLintrinsec |

Kload |

|

|

CK → Q |

0.729 ns |

4104 |

0.732 ns |

5654 |

|

CK → QN |

0.359 ns |

4600 |

0.597 ns |

7974 |

D 555g68f eterminarea parametrilor de constrangere si durata minima a pulsului

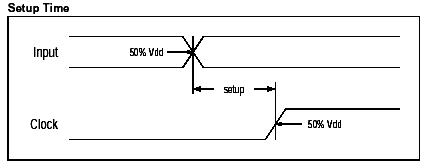

Setup_time este timpul minim dinaintea frontului activ de ceas in care este obligatoriu ca semnalul de intrare sa fie stabil (sa nu se inregistreze tranzitii). Pentru determinarea acestui timp se va face o analiza parametrica asupra componentei « td » a semnalului pulse de pe intrarea K. Acesta variabila va lua valori de timp apropiate de momentul unui front activ de ceas. Pentru fiecare valoare de timp se va urmari comportarea iesirii.

D 555g68f in datele de proiectare trebuie ca timpul de tranzitie (TR) al semnalelor aplicate la intrare, sa fie din domeniul (20ps..50ps). Se alge TR= 30ps.

Pentru realizarea simularii se foloseste:

*determinarea parametrilor de constrangere

.inc JKFFS.cir

XJKFFS 1 2 3 4 5 6 7 JKFFS

VCK 4 0 pulse(0 2ns 2.5ns 5ns)

*VSN 1 0 pulse(0 0 40ns 80ns)

*VJ 2 0 pulse(0 0.5ns 12ns 24ns)

VK 3 0 pulse(0 10ns 20ns)

VJ 2 0 5

VSN 1 0 5

Vdd 7 0

CQ 5 0

CQN 6 0

.param CL 0.1p

.param TR 30p

.param Vdd 5

.param Td 6.8ns

.step param Td LIST 6.6n 6.7n 6.8n 6.9n

.inc D 555g68f :scoalapacproiectCMOS_AMIS_050_T49M.TXT

.TRAN 0.1ns 10ns 5ns 0.1ns

.PROBE

.END 555g68f

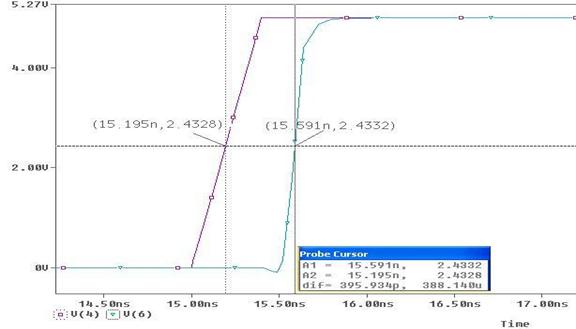

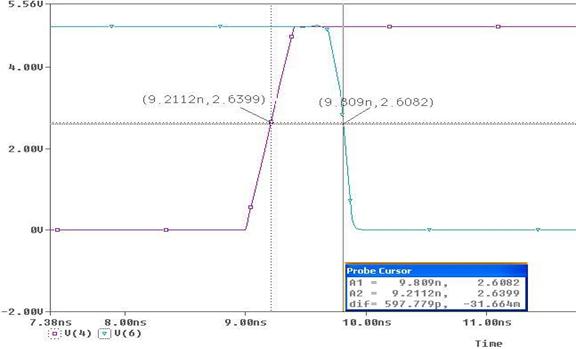

Se observa ca prin varierea lui Td la intrarea K de la 6.9 la 7 iesirea Q se modifica:

SETUP_TIME_LHà CK = 99 ps

Se observa ca prin varierea lui Td, al intrarii K de la 6.8n la 6.9n iesirea Q se modifica:

SETUP_TIME_HLà CK = 70 ps

Hold_time este timpul minim de dupa frontul activ de ceas in care este obligatoriu ca semnalul de intrare sa fie stabil (sa nu se inregistreze tranzitii). Pentru determinarea acestui timp se va face o analiza parametrica tot asupra componentei « td » a semnalului pulsatoriu de pe intrarea K. D 555g68f e data aceasta valorile lui « td » vor fi momente de timp de dupa frontul activ, apropiate de acesta.

D 555g68f in datele de proiectare trebuie ca timpul de tranzitie (TR) al semnalelor aplicate la intrare, sa fie din domeniul (20ps..50ps). Se alge TR= 30ps.

Se observa ca prin varierea lui Td, al intrarii K iesirea Q nu se modifica atat pe front pozitiv, cat si pe cel negativ (circuitul functioneaza corect)

HOLD 555g68f _TIME_LHà CK = 0s

HOLD 555g68f _TIME_HLà CK = 0s

Pentru determinarea parametrului minpw_high se face o analiza parametrica dupa "pw" din semnalul de clock de tip pulse. Acesta se va micsora pana cand iesirea nu mai urmareste tranzitiile intrarii:

Pentru realizarea simularii se folseste:

*minpw_high

.inc JKFFS.cir

XJKFFS 1 2 3 4 5 6 7 JKFFS

VCK 4 0 pulse(0 3ns 10ns)

*VSN 1 0 pulse(0 0 40ns 80ns)

*VJ 2 0 pulse(0 0.5ns 12ns 24ns)

VK 3 0 pulse(0 0.5ns 16ns 32ns)

VJ 2 0 5

*VK 3 0 0

VSN 1 0 5

Vdd 7 0

CQ 5 0

CQN 6 0

.param CL 0.1p

.param TR 30p

.param Vdd 5

.param pw 0.2n

.step param pw LIST 0.231n 0.232n 0.233n

.inc D 555g68f :scoalapacproiectCMOS_AMIS_050_T49M.TXT

.TRAN 0.1ns 100ns 40ns 0.1ns

.PROBE

.END 555g68f

Prin varierea lui pw a semnalului de CK se observa ca pentru valori mai mici de 0.231n iesirea nu mai urmareste tranzitiile intrarii.

MINPW_HIGH=0.232ns

Pentru determinarea parametrului minpw_low se face o analiza parametrica dupa "per" din semnalul de clock de tip pulse (se variaza perioada semnalului de CK). Acesta se va micsora pana cand iesirea nu mai urmareste tranzitiile intrarii.

Pentru realizarea simularii se foloseste:

*minpw_low

.inc JKFFS.cir

XJKFFS 1 2 3 4 5 6 7 JKFFS

VCK 4 0 pulse(0 3ns 5ns )

*VSN 1 0 pulse(0 0 40ns 80ns)

*VJ 2 0 pulse(0 0.5ns 12ns 24ns)

VK 3 0 pulse(0 0.5ns 16ns 32ns)

VJ 2 0 5

*VK 3 0 0

VSN 1 0 5

Vdd 7 0

CQ 5 0

CQN 6 0

.param CL 0.1p

.param TR 30p

.param Vdd 5

.param per 5n

.step param per LIST 5.191n 5.192n 5.193n

.inc D 555g68f :scoalapacproiectCMOS_AMIS_050_T49M.TXT

.TRAN 0.1ns 100ns 0.1ns

.PROBE

.END 555g68f

Prin varierea perioadei semnalului de ck se observa ca pentru valori mai mici de 5.192n iesirea nu mai urmareste corect tranzitiile intrarii.

MINPW_LOW=5.192n

|

Pin intrare |

Parametru constrangere |

D 555g68f urata interval [ns] |

|

K |

SETUP_TIME_LH → CK |

99p |

|

SETUP_TIME_HL → CK |

70p |

|

|

HOLD 555g68f _TIME_LH → CK | ||

|

HOLD 555g68f _TIME_HL → CK | ||

|

CK |

MINPW_HIGH |

0.232n |

|

MINPW_LOW |

5.192n |

PARTEA II - VHD 555g68f L

A. i) Model comportamental pentru circuitul proiectat si analizat dinamic.

library ieee;

use ieee.std_logic_1164.all;

entity jkffs is

generic( tp_LHQ :time:= 0.729 ns;

tp_HLQ :time:= 0.732 ns;

tp_LHQN :time:= 0.359 ns;

tp_HLQN :time:= 0.597 ns

);

port (ck: in std_logic;

j: in std_logic;

k: in std_logic;

sn: in std_logic;

q, qn: inout std_logic

);

end jkffs;

architecture bistabil of jkffs is

begin

process (ck, j, k, sn)

begin

if sn='0' then q<='1'; qn<='0';

elsif sn='1' and ck'event and ck='1' then

if j='0' and k='0' then

q<=q; qn<= not q;

elsif j='0' and k='1' then

q<='0' after tp_HLQ;

qn<= '1' after tp_LHQN;

end if;

if j='1' and k='1' then

q<= not q; qn<= q;

elsif j='1' and k='0' then

q<='1' after tp_LHQ;

qn<= '0' after tp_HLQN;

end if;

else q<= q; qn<= not q;

end if;

end process;

end bistabil;

ii) Entitate de test care simuleaza modelul de la punctul i)

library ieee;

use ieee.std_logic_1164.all;

entity Test_jkffs is

end Test_jkffs;

architecture test_bistabil of Test_jkffs is

signal T_ck, T_j, T_k, T_sn: std_logic;

signal T_q, T_qn: std_logic;

component jkffs is

port(ck: in std_logic;

j: in std_logic;

k: in std_logic;

sn: in std_logic;

q, qn: inout std_logic);

end component;

begin

UUT: jkffs port map(ck=>T_ck, j=>T_j, k=>T_k, sn=>T_sn, q=>T_q, qn=>T_qn);

gen_ck: process

begin

T_ck<='0';

wait for 1 ns;

T_ck<='1';

wait for 1 ns;

end process;

gen_sn: process

begin

T_sn<='1';

wait for 30 ns;

T_sn<= '0';

wait for 20 ns;

end process;

gen_j: process

begin

T_j<='0';

wait for 3 ns;

T_j<='1';

wait for 3 ns;

end process;

gen_k: process

begin

T_k<='0';

wait for 4 ns;

T_k<='1';

wait for 4 ns;

end process;

end test_bistabil;

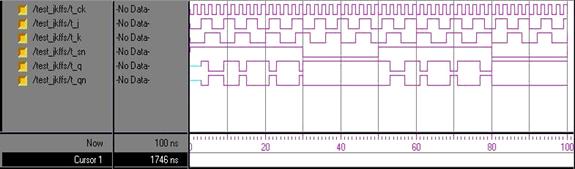

Formele de unda rezultate sunt prezentate in figura:

|