CIRCUITE COMBINATIONALE

Sunt circuitele de comanda la care setul marimilor de iesire este determinat univoc de setul marimilor de intrare

Relatiile dintre marimile de intrare si iesire

Y1=f1(n1,..,nn)

Ym =fm(n1,..nm) n ,f-functii logice

Absenta memoriei face ca aceste circuite sa nu depinda de timp

Din categoria lor fac parte :decodificatoarele

DECODIFICATOARELE sunt un CLC care reaalizeaza decodificarea informatiei din binar in zecimal sau alt cod ;cu cu n intrari si 2 n iesiri.

* Rolul decodificatoprelor este acela ca din 4 combinatiii ale valorilor marimilor de intrare sa selecteze la cele 4 iesiri cate o combinatie distincta folosind o matrice de referinta .

|

A1,a2 |

0 |

1 |

|

O |

1 |

0 |

|

1 |

0 |

0 |

|

A1,A2 |

0 |

1 |

|

0 |

Y1 |

Y2 |

|

1 |

Y3 |

Y4 |

|

A2A1/A4 A3 |

00 |

01 |

11 |

10 |

|

00 |

0 |

1 |

3 |

2 |

|

01 |

4 |

5 |

7 |

6 |

|

11 |

x |

x |

x |

x |

|

10 |

8 |

9 |

x |

x |

![]()

![]()

![]()

![]()

0= A1 A2 A3 A4

![]()

![]()

1=A1 A2 A3 A4

![]()

![]()

![]()

2= A1 A2 A3 A4

![]()

3=A1 A2 A 3 A4

![]()

![]()

![]()

4=A1 A2 A3 A4

![]()

![]()

5=A1 A2 A3 A4

![]()

![]()

6=A1 A2 A3 A4

![]()

7=A1 A2 A3 A4

![]()

8=A1 A2 A3 A4

![]()

![]()

![]()

9=A1 A2 A3 A4

CIRCUITE BASCULANTE BISTABILE

Circuitele basculante bistabile (CBB) fac parte din marea familie a circuitelor logice secventiale (c.l.s),cunoscute in literatura si sub denumirea de sisteme de ordin>1.Trecerea de la sistemele de ordin zero(c.l.c) la cele de ordin superior se face prin introducerea unor reactii care-i confera sistemului proprietatea de "memorie".Astfel, iesirile circuitului secvential sunt partial independente de semnalele de intrare din acel moment , depinzand -tot partial- de starile anterioare ale circuitului.

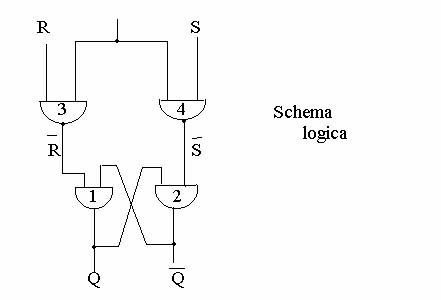

Circuitul basculant bistabil RS

CBB-RS se obtine prin introducerea unei reactii intr-un sistem elementar de ordin zero.Sistemul astfel obtinut este de ordin 1.

CBB-RS poate fi realizat in varianta asinocra,sincrona sau "Master-Slave"(stapan-sclav)

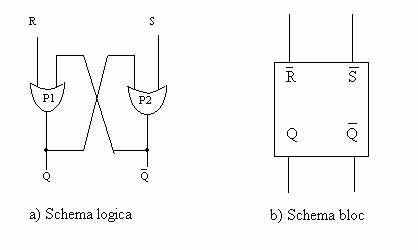

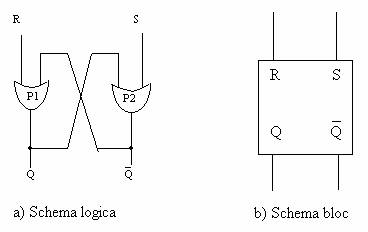

CBB-RS asincron

CBB-RS asincron,cunoscut-datorita proprietatilor sale de a memora-si sub denumirea de"lach"

(zavor) poate fi realizat cu NOR-uri sau cu NAND-uri.

In varianta NOR, fig. 16.1,functionarea circuitului este ilustrata de tabelul de tranzitie, tab.1, in care s-a notat cu indice"n"-valoarea logica prezentata si cu "n+1"-valoare logica viitoare.

Astfel,pentru Rn S n=00(prima linie a tabelului de tranzitie)portile P si P sunt valide si valoarea logica a lui Qn(Qn) de la iesirea portii P1si (P ) ajunge la iesirea portii P (P ) sub forma Qn(Qn).Observam ca valorile logice ale iesirilor raman neschimbate, deci Qn+1+Qn

Pentru Rn Sn+ 01 (Rn=0, Sn=1),iesirea portii va fi:

Qn =Q n+ Sn= Qn +1=1=0

Deci la intrarea portii P se aplica Rn=0 si Qn=0.Eviden, la iesirea portii P , vom avea:

Qn+1=Rn+Qn=0+0=0+1

Prin urmare atunci cand intrarea S este active (Sn=1), se realizeaza inscrierea unui"1"logic in memorie.Denumirea"S" a intrarii este o prescurtarea cuvantului"SET" din limba engleza care inseamna"inscriere".

Pentru RnSn=10 (Rn=1, Sn=0),se poate demonstra-urmarand o cale similara celei de mai sus-ca se obtine Qn+1=0

Rezulta ca activarea intrarii R(Rn=1),conduce la stergerea informatiei din memorie, echivalent cu punerea pe"0" a memoriei.Denumirea"R"a intrarii este o prescurtare a cuvantului "RESET" din limba engleza care inseamna"stergere".

Pentru RnSn=11 iesirile celor doua porti sunt fortate simultan in "0" logic,Qn+1=Qn+1=0.

Din acest motiv combinatia de intrare 11 este interzisa (de obicei prin logica suplimentara) iar in locatia corespunzatoare din tab.16.1 se punde semnul "x" specific locatiilor in care functia este nedefinita.

Pentru a obtine o forma minima a functiei de iesire,construim diagrama Veitch-Karnaugh(VK)a circuitului, fig, 16.2, si, dupa grupari convenabile obtinem:

Qn+1=Sn+RnQn.

Relatia(16.4)se verifica numai pentru primele trei linii ale tab.16.3,functionarea circuitului este ilustrata in tabelul de tranzitie,tab.16.2,ir minimizarea functiei de iesire este realizata cu ajutorul diagramei VK,fig.16.4.

Observam ca in urma minimizarii se obtine aceeasi expresie(16.4)pentru Qn+1.

CBB-RS asincron, indifferent de varianta de implementare adoptata, prezinta urmatoarele deficiente:

-aceleasi semnale care indica modul CUM (in care)trebuie sa se faca comutarea,dicteaza si momentul CAND trebuie sa aiba loc aceasta;

-pentru anumite tranzatii ale intrarilor circuitului,starea iesirilor este imprevizibila.

Exemplu:Tranzatia 11-00 a intrarilor,poate aduce iesirile Q,Q aleCBB din fig.16.1 in oricare din cele doua stari posibile.Astfel,pentru RnSn=11, vom avea Q=Q=0 si portile P ,P vor fi validate.Pentru RnSn=00, admitand ca poarta P este mai rapida, se va obtine un "l" logic la iesirea Q,ceea ce forteaza-prin reactie-un "0"logic la Q.Evident, daca aplicam aceeaci supozitie pentru poarta P , VALORILE LOGICE ALE IESIRILOR SE INVERSEAZA.

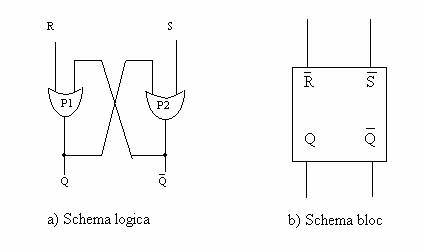

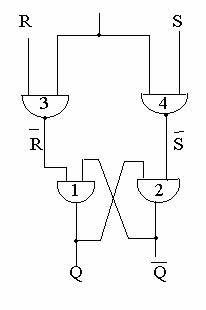

CBB-RS.sincron

CBB-RS sincron se obtine din CBB-RS asincron prin adaugarea a doua porti(3 si 4) validabile de un impuls de tact(fig. 16.5 si 16.6).

Functionarea celor doua CBB-RS sincrone fiind similara, ne vom limita la explicarea functionarii din fig.

Observam ca pentru CLK=1, portile 3 si 4 sunt inhibate si orice modificare a lui R,S nu va afecta CBB-ul SR asincron format din portile 1si 2.

Intr-adevar, intrarile acestuia prin CLK=1 vor fi 00 si ,conform primei linii din tab 16.1 iesirile vor ramane neschimbate.

Cand CLK=0,portilw 3si4 sunt valide si intrarile R S,transformate in RS,vor avea acces la CBB-RS asincron,actionand conform tab. 16.1.

Pentru o functionare sincrona a circuitului este necesar ca impulsul de CLK care dicteaza CAND sa se execute comenzile R S, sa apara numai dupa ce acestea s-au stabilizat.

Modificarea lui R S in intervalul de timp in care portile de intrare 3,4 sunt deschise,conduce la o functionare asincrona a circuitului.Din acest motiv,sunt necesare conditii restrictive pentru relatia de timp CLK si R S.

Circuitul din fig. 16.6 functioneaza similar, impulsul de tact fiind de aceasta data active pe palierul"l" logic.

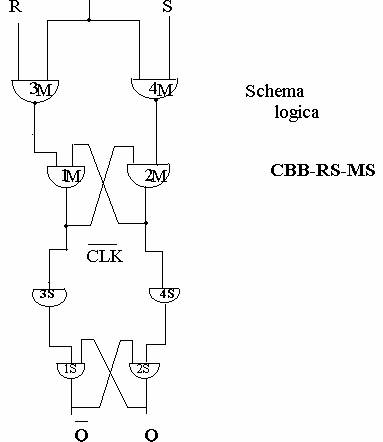

CBB-Rs-"Master-Slave"

Dupa cum reiese din fig. 16.7,CBB-RS-MSreprezinta o extensie serie a bistabilului RS sincron implemantat cu NAND-uri(v.fig.16.6).Schema logica este prezentata in fig. 16.8a, iar diagramele CLK siCLK- in figura 16.8b si c.

In intervalul(1)-(2),portile de intrare(3M,4M)si de transfer(3S,4S)sunt blocate iar MASTER-ul este izolat atat de intrari cat si de SLAVE.

In intervalul(3)-(4)se repeat situatia sin intervalul (1)-(2) cand MASTER-ul era izolat atat

de intrari cat si de SLAVE.

In sfarsit,dupa momentul(4),portile3M,4M sunt blocate (MASTER-ul izolat fata de intrari) iar portile 3S,4S sunt valise si informatia din MASTER se transfera in SLAVE.

Concluzionand ,inscrierea informatiei in MASTER are loc inainte de momentul(3) (posibil chiar pe frontal descrescator al CLK),iar transferal ei in SLAVE (si deci la iesire) are loc dupa momentul(4) (deci pe acelasi front descrescator al CLK).

Prin urmare, pentru inscrierea fara erori a informatiei in CBB-RS-MS,este necesar ca aceasta sa ramana stabile la intrare un interval de timpin jurul intervalului(3)-(4).

CBB-RS-MS nu elimina posibilitatea tranzitiilor nedeterminate .

Evident, se pot construe CBB-RS-MS care sa comute pe tranzitia pozitiva a impulsului de tact.

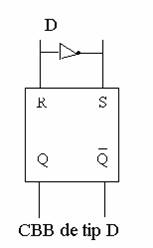

Circuitul basculant bistabil de tip D

CBB de tip D asincron

![]() Se obtine

dintr-un CBB-RS asincron ,prin atasarea unui inversor in scopul eliminarii

starilor nedeterminate.

Se obtine

dintr-un CBB-RS asincron ,prin atasarea unui inversor in scopul eliminarii

starilor nedeterminate.

Datorita inversorului, raman numai liniile pentru care Dn= Sn=Rn,deci liniile 2 si 3.

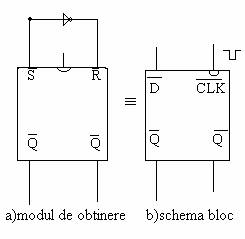

CBB de tip D sincron

CBB de tip D sincron se obtine dintr-un CBB-RS sincron,tot prin atasarea unui inversor.

![]()

Ca si in cazul CBB-RS sincron, pentru a comuta sincronizat de CLK este necesar ca informatia de la intrarea D sa se modifice in afara palierului active al impulsului CLK,in timpul palierului respectv ea ramanand stabila.Aparitia palierului activ al impulsului de CLK transfera la iesire informatia de la intrarea bistabilului .Spunem ca se realizeaza o "temporizare comandanta prin CLK".De fapt,denumirea de bistabil de tip D,provine din englezesculDELAY=intarziere .

Bistabilul de tip D sincron are numeroase aplicatii practice dintre care amintim:latch-ul adresabil,memoria RAM,etc.

CIRCUITUL BASCULANT BISTABIL DE TIP JK

Reamintim faptul ca bistabilul D a aparut ca urmare a necesitatii de a inlatura tranzitiile nedeterminate ale bistabilelor RS.Acelasi effect de eliminare a tranzitiilor nedeterminate se poate obtine prin introducerea de reactii suplimentare in structurile RS.

Acestea sunt de 2 feluri:

-CBB-JK asincron , care poate fi obtinut din bistabilul RS asincron prin introducerea unei reactii.

-CBB-JK Master Slave ,care se obtine prin conectarea in cascada a 2 CBB-JK sincrone.

|

Jn |

Kn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

CONVERSIA CIRCUITELOR BISTABILE RS,D,T SI JK

In numeroase aplicatii este necesara utilizarea unui anumit tip de CBB,practic fiind disponibil un altul .In aceste conditii, de mare ajutor sunt ecuatiile logice de legatura dintre diferite tipuri de bistabile , relatii ce se pot obtine pe baza unui table comparative.

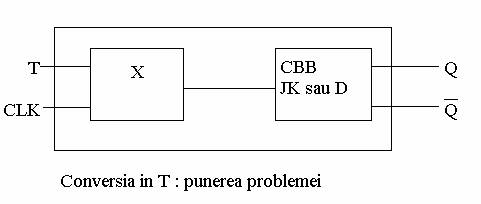

Conversia in T

Pentru realizarea conversiei JK- T sau D T, trebuie gasita relatia dintre intrarea T a bistabilului simulate si intrarile JK sau D ale bistabilului disponibil.

Pentru aceasta se construieste tabelul ajutator , astfel:in primele 2 coloane se trec toate combinatiile logice posibile ale intrarii (Tn) si starii(Qn) bistabilului simulate, in urmatoarele 2 coloane-valorile logice ale intrarilor JnKn si Dn, completate numai dupa trecerea in ultima coloana a valorilor logice ale iesirii Qn+1 a bistabilului

simulate

Completarea cu valorile logice corespunzatoare a coloanelor Jn,Kn,si Dn se face pornind de la valorile logice ale starii prezente si viitoare (Qn si Qn-1) .

|

Tn |

Qn |

JnKn |

Dn |

Qn+1 |

|

0 |

0 |

0x |

0 |

0 |

|

0 |

1 |

x0 |

1 |

1 |

|

1 |

0 |

1x |

1 |

1 |

|

1 |

1 |

x1 |

0 |

0 |

Astfel, situatia Qn=0, Qn+1=0, se obtine atunci cand JnKn=00 sau 01, deci JnKn =0x,prin "x" intelegem "indiferent". Qn=0, Qn+1=0, se obtine atunci cand JnKn=00 sau 10, deci JnKn =x0, s.a.m.d .

Odata completat tabelul, se poate trece la sinteza, construind diagramele VK pentru functiile de iesire Jn ,Kn , Dn .

|