1. Tema proiectului

Sa se proiecteze un modul calculator monoplaca SBC cu microprocesor 8086, cu posibilitati de cuplare într-o configuratie multimicroprocesor cu magistrala MULTIBUS si având urmatoarele caracteristici:

u memorie EPROM de 64 Ko cu circuite 2764

u memorie SRAM de 8 Ko cu circuite 2114

u memorie DRAM de 16 Ko cu circuite 2104A

u interfata I/O cu circuite 2x8282.

Pentru tratarea înteruperilor se va folosi circuitul 8259A. În cazul circuitelor programabile se vor prezenta secventele de program pentru aducerea acestora în stare operationala. Se cere schema electrica a modului, realizata cu un program de proiectare asistata de calculator.

2. Schema bloc a modulului

Schema bloc a modulului contine urmatoarele elemente:

Microprocesorul (8086) care lucreaza la modul maximal.

Generatorul de tact (8284) folosit pentru generarea tactului necesar microprocesorului pentru a asigura functionarea circuitelor interne ala acestuia. Circuitul (8284) face divizarea cu trei a frecventei determinate de cuartul ce se conecteaza la el.

Controler de magistrala (8288) care, prin decodificarea semnalelor de stare (S0,S1,S2) furnizeaza semnalele de comanda corespunzatoare.

Latch de adrese (8282), pentru generarea magistralei interne de adrese, realizata prin demultiplexarea semnalelor AD0-A 929t1913j D15 si A16-19.

Buffer de date (8286), pentru generarea magistralei interne de date , realizata prin demultiplexarea semnalelor AD0-AD15.

Un bloc de memorie EPROM (2764).

Un bloc de memorie SRAM (2114).

Un bloc de memorie DRAM (2104A).

Decodificator de adresa (8205) pentru selectarea blocurilor de memorie.

Controler de reîmprospatare (8202) pentru reîmprospatarea blocului de memorie DRAM.

Circuite de interfata I/O (2x8282) si Conectorul de interfete pentru conectarea sistemului cu exteriorul.

Bloc de interfata cu Magistrala Sistem care face legatura dintre modul si sistemul multimicroprocesor. Blocul este format din

a). Arbitru de magistrala (8289).

b).Controler de magistrala (8288).

c). Buffer de date (8287).

d).Latch adrese (8283).

Controler de întreruperi (8259).

Conector de magistrala multibus.

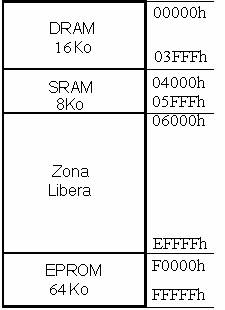

3. Repartizarea spatiului de adrese

Microprocesorul 8086 dispune de un spatiu de memorie de 1 Mo si separat de un spatiu de adrese I/O de 64 Ko.

Pentru ca modulul calculator monoplaca SBC foloseste microprocesorul 8086 memoria locala va trebui sa aiba o zona care sa înceapa la adresa 00000h pentru tabelul vectorilor de întrerupere si va trebui ca la adresa de restart sa fie o memorie EPROM si anume la adresa FFFF0h, iar pentru interactiunea cu celelate module din sistem se vor folosi module de memorie.

Memoria EPROM:

- ocupa 64 Ko din spatiul memoriei totale. Se utilizeaza circuite 2764 care au capacitatea de 8 Ko, deci se utilizeaza 8 circuite de acest tip.

Memoria RAM DIAMICĂ:

- ocupa 16 Ko din spatiul memoriei totale.Se utilizeaza circuite 2104A care au capacitatea de 4096x1 bit , deci se utilizeaza 32 circuite de acest tip.

Memoria RAM STATICĂ:

- ocupa 8 Ko din spatiul memoriei totale. Se utilizeaza circuite 2114 care au capacitatea de 1024x4 bit , deci se utilizeaza 16 circuite de acest tip.

Harta memoriei:

Spatiul de memorie vom folosi astfel:

zona 00000h - 03FFFh pentru memoria DRAM (16Ko)

zona 04000h - 05FFFh pentru memoria SRAM (8Ko)

zona 06000h - EFFFFh zona libera

zona F0000h - FFFFFh pentru memoria EPROM (64Ko)

Harta memoriei va arata în felul urmator:

4. Proiectarea unitatii centrale

Deoarece

trebuie proiectat un sistem MULTIBUS, microprocesorul lucreaza în regim

maxim (intrarea ![]() ), ceea ce face ca microprocesorul sa genereze semnalele

de comanda prin intermediul controlerului de magistrala 8288,

caruia îi livreaza un cuvânt de stare

), ceea ce face ca microprocesorul sa genereze semnalele

de comanda prin intermediul controlerului de magistrala 8288,

caruia îi livreaza un cuvânt de stare ![]() , prin decodificarea caruia controlerul genereaza

semnalele de comanda necesare bunei functionari a sistemului (

, prin decodificarea caruia controlerul genereaza

semnalele de comanda necesare bunei functionari a sistemului (![]() etc. ).

etc. ).

Pentru generatorul de tact se foloseste circuitul 8284, acelasi circuit furnizând, pe lânga semnalul de tact CLK si semnalul de RESET. Frecventa cristalului conectat la acest circuit este de 15MHz care se divide în trei, rezultând frecventa de lucru a mprocesorului.

Se tine cont de faptul ca microprocesorul 8086 are o magistrala unica atât pentru date cât si pentru adrese, ceea ce face necesara demultiplexarea acesteia în exterior, prin intermediul circuitelor 8282 si 8286.

5. Proiectarea memoriei

La proiectarea memoriei se pune problema timpului de acces al memoriei. Tabelul urmator contine timpii de acces ale circuitelor de memorie folosite în proiectare.

|

Circuit |

Timp de acces |

|

2764 (EPROM) |

200 ns |

|

2114 (SRAM) |

150 ns |

|

2104A (DRAM) |

225 ns |

Se constata ca nu este necesara introducerea starilor WAIT pentru ca timpul maxim de acces acceptat de catre mprocesor este de 500ns.

În

cazul memoriei DRAM sincronizarea transferului de date se realizeaza cu

semnalul ![]() , care legat la intrarea RDY1 al circuitului 8284 va

forta generarea starilor WAIT necesare.

, care legat la intrarea RDY1 al circuitului 8284 va

forta generarea starilor WAIT necesare.

A) Memoria EPROM (64Ko): cu circuite 2764 (8Kx8BIT)

- vom avea 8 circuite de câte 8Ko si fiind ca în sistemele cu mP 8086 memoria este organizata pe bancuri.

|

A19A18A17A16A15A14 |

A13A12A11A10A9A8A7A6A5A4A3A2A1 |

A0 |

Adresa în HEXA |

Semnal De selectie |

|

1 1 1 0 0 1 1 1 0 0 |

0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 |

F0000 F3FFF |

EPROM1 |

|

|

1 1 1 0 1 1 1 1 0 1 |

0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 |

F4000 F7FFF |

EPROM2 |

|

|

1 1 1 1 0 1 1 1 1 0 |

0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 |

F8000 FBFFF |

EPROM3 |

|

|

1 1 1 1 1 1 1 1 1 1 |

0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 |

FC000 FFFFF |

EPROM4 |

B) Memoria DRAM (16 Ko): cu circuite 2104A (4096x1BIT):

- vom avea, în total 32 circuite 2104A, dintre care primul 16 va forma bancul inferior iar celalalt 16 va forma bancul superior.

|

A19 A18 A17 A16 A15 A14 A13 |

A12......A4 A3 A2 A1 |

A0 |

Adresa în HEXA |

Semnal De selectie |

|

0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

0 ... 0 0 0 0 1 ... 1 1 1 1 |

00000h 01FFFh |

DRAM0 |

|

|

0 0 0 0 0 0 1 0 0 0 0 0 0 1 |

0 ... 0 0 0 0 1 ... 1 1 1 1 |

02000h 03FFFh |

DRAM1 |

Pentru reîmprospatarea memoriilor dinamice se utilizeaza controlerul de reîmprospatare 8202. Cuartul atasat din exterior controlerului are frecventa de 25 MHz.

C) Memoria SRAM (8 Ko): cu circuite 2114 (1Kx4BIT):

- în cazul acesta vom avea 16 circuite 2114, care vor fi selectate cu ajutorul semnalelor SRAM1, SRAM2, SRAM3 si SRAM4.

|

A19A18A17A16A15A14A13A12A11 |

A10A9A8A7A6A5A4A3A2A1 |

A0 |

Adresa în HEXA |

Semnal De selectie |

|

0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 |

0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 |

047FF |

SRAM1 |

|

|

0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 1 |

0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 |

04FFF |

SRAM2 |

|

|

0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 0 1 0 |

0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 |

057FF |

SRAM3 |

|

|

0 0 0 0 0 1 0 1 1 0 0 0 0 0 1 0 1 1 |

0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 |

05FFF |

SRAM4 |

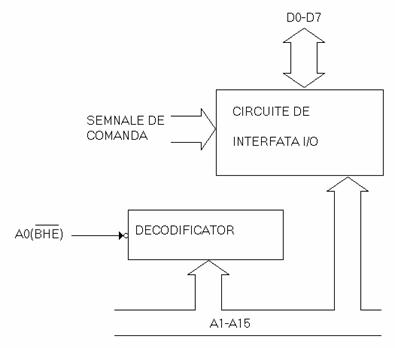

6. Proiectarea interfetelor de I/O

Toate circuitele fiind plasate la adrese pare acestea au fost conectate la liniile D0-D7 ale magistralei iar bitul A0 a fost utilizat la selectia circuitului împreuna cu semnalele corespunzatoare venite de la decodificator.

|

Adresa 0000H |

|

Adresa 0002H |

|

Adresa 0001H (iesire octet inferior) |

|

Adresa 0004H iesire octet superior |

|

Adresa 0006H iesire cuvânt |

Semnalele de comanda utilizate sunt cele specifice adresarii în spatiul de intrare-iesire.

Circuitul 8259 este plasat la adrese pare deci vor fi conectate la D0-D7.

Deoarece numarul de circuite este redus se

utilizeaza o selectie liniara. Semnalele de comanda

utilizate pentru citire si scriere sunt ![]() respectiv

respectiv ![]() .

.

Circuitele 8282 sunt selectate ca iesiri pe octet inferior, octet superior sau un întreg cuvânt.

Circuitul 8259A este controler de întreruperi. Modul în care se conecteaza nivelele de întrerupere ale lui 8259A la liniile de întrerupere ale magistralei MULTIBUS si la sursele locale de întrerupere este lasat la latitudinea utilizatorului.

Elaborarea secventei de program pentru circuitele programabile

Circuitul 8259A se programeaza în mod singular intrari active pe nivel întreruperi vectorizate achitare automata a întreruperii prioritatile rotitoare.

Secventa de program pentru 8259A este urmatoarea:

MOV AL,1Bh

OUT 02h,AL

MOV AL,38h

OUT 02h,AL

MOV AL.0Fh

MOV

OUT 02h,

Programul pentru circuite 8282:

MOV A,0000h

OUT 0002h,A

MOV A,VECT

RETN

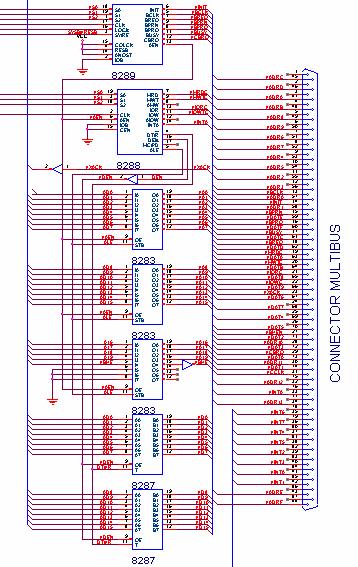

8. Blocul de interfata cu magistrala MULTIBUS

Acest bloc contine arbitrul de magistrala (8289), controler magistrala (8288), latchuri (8287) si buffer de date (8283)

Circuitele

8283 si 8287 realizate cu inversoare sunt utilizate pentru a asigura

compatibilitatea semnalelor interne cu celor de pe magistrala MULTIBUS. Cererea

la magistrala MULTIBUS este semnalizata când semnalul ![]() =1. Arbitrul de magistrala si controlerul de

magistrala decodifica cuvântul de stare

=1. Arbitrul de magistrala si controlerul de

magistrala decodifica cuvântul de stare ![]() furnizat de mprocesor

si genereaza semnalele de comanda pe magistrala MULTIBUS.

furnizat de mprocesor

si genereaza semnalele de comanda pe magistrala MULTIBUS.

9. Schema finala

Schema finala a modulului SBC cu microprocesor 8086 este data în anexa.

|