Circuite logice combinationale

Generalitati

In cadrul circuitelor logice combinationale se incadreaza mai multe feluri de circuite

Unul dintre aceste tipuri de circuit fiind acela integrat care cuprinde: Demultiplexorul si Multiplexorul. Acestea fiind circuite integrate pe scara medie.

Functionarea Demultiplexoarelor si a Multiplexoarelor se face prin transmiterea mai multor informatii pe acelasi canal; cum aceste doua operatii nu se pot face simultan,se recurge la o partajare in timp a canalului, numita multiplexare, iar operatia inversa fiind numita demultiplexare.

Multiplexorul

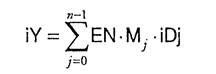

Multiplexorul este un comutator digital care transmite la iesire datele provenite de la una din cele n surse disponibile. Figura 1(a) prezinta intrarile si iesirile unui multiplexor de b biti cu n intrari. Exista n surse date, deci fiecare de b biti de iesire. Exista s intrari cu care se pot selecta cele nsurse ,deci s=[log n]. O intrare de activare EN permite ca multiplexorul sa actioneze corespunzator; cand EN=0, toate iesirile sunt 0. Adesea denumirea "multiplexor" este prescurtata mux. Figura 1(b) prezinta un circuit cu comutatoare echivalent, in linii mari, cu un multiplexor. Insa ,spre deosebire de circuitul cu comutatoare mecanice, multiplexorul este un dispozitiv unidirectional: informatiile circula dinspre intrari (in stanga) spre iesiri (in dreapta) .

Putem scrie o ecuatie logica generala pentru iesirea unui multiplexor:

Figura 4.1 Structura de multiplexor: (a) intrarile si iesirile; (b)circuit echivalent functional.

Simbolul de insumare semnifica suma logica a unor termini produs. Variabila iY este un anumit bit de iesire (1< i <b) ,iar variabila iDj este bitul de intrare i de la suma j(0< j < n-1). Mj reprezinta mintermenul j corespunzator celor s intrari de selectare. Prin urmare ,cand multiplexorul este activat si valoarea de la intrarile de selectare este j, fiecare iesire iY este egala cu bitul corespunzator al intrarii selectate ,iDj.

Este evident ca multiplexoarele sunt dispositive utile in orice aplicatie in care datele trebuie transferate in mai multe surse catre o singura destinatie.

Functia unui multiplexor este de a transmite datele de la una la alta din cele m cai de intrare la o cale de iesire unica. Selectarea se face prin intermediul unui cuvant binar de selectie cu n biti. Intre numerele m si n exista relatia m=2n Schema bloc a unui MUX este prezentata in fig. 4.2(a) ,iar schema de desfasurata a unui MUX cu 8 intrari de date si o intrare de validare este desenata in fig. 4.2(b).

tipuri de MUX utilizate in mod current sunt:

-MUX cu 16 intrari de date (74150), cu o intrare de validare si o iesire ambele fiind active pe 0;

-MUX cu 8 intrari de date (74151), cu o intrare de validare active pe 0si doua iesiri complementare;

-MUX cu 8 intrari de date (74152), fara intrare de validare si cu o singura iesire complementara

-MUX cuadruplu cu cate 2 intrari de date (74157), cu logica de selectie si validare comuna si cu cate o iesire necomplementata.

Implementarea sistematica a circuitului MUX (simplificat pana la 4 intrari) este dat in fig.3 (a), obtinut prin sinteza functiei f conform expresiei:

: 3(a): Multiplexor cu 4 intrari digitale.

Pentru generarea semnalelor deintrare (D0-D3),a celor de comanda (A si B)si semnalul de activare (E) se va utilize Generatorul de cuvinte (Word Generator).

Cand A=0, B=0 rezulta A'xB'=1 si se selecteaza linia D0-la iesire ajunge semnalul de la intrarea D0;

Cand A=0,B=1 rezulta A'xB=1 si se selecteaza linia D1(cazul din fig.3(a)), etc.

Daca E=1 se inhiba operatia intregului sistem.

Tabelul de functionare a MUX-ului:

|

Activare |

Semn de control |

Iesire |

|

|

E |

A |

B |

F |

|

|

|

|

D0 |

|

|

|

|

D1 |

|

|

|

|

D2 |

|

|

|

|

D3 |

|

|

X |

X |

inhibare |

Aceasi,functionare a unui MUX cu 8 intrari poate fi studiat utilizand circuitul din fig.3(b),ce reprezinta un multiplexor cu 8 intrari (D0-D7) si o iesire -Y(f),cu trei linii de control A,B,Csi semnal de activare G'(E).

3(b).MUX - o iesire la 8 intrari.

Tabelul de functionare a MUX-ului din fig.3(b)

|

Activare |

Semnale de control |

Iesire |

||

|

E |

A |

B |

C |

F |

|

|

|

|

|

D0 |

|

|

|

|

|

D1 |

|

|

|

|

|

D2 |

|

|

|

|

|

D3 |

|

|

|

|

|

D4 |

|

|

|

|

|

D5 |

|

|

|

|

|

D6 |

|

|

|

|

|

D7 |

|

|

X |

X |

X |

inhibare |

Extinderea capacitatii de multiplexare (selectie) se obtine folodind un numar corespunzator de MUX standard, validate succesiv prin intermediul unui DCD ,ale caror iesiri sunt insumate. In fig.4 este exemplificata extinderea capacitatii de multiplexare a MUX 74150 de la 16 cai la 64 de cai. Se constata ca extinderea capacitatii de selectie de 2k ori necesita k linii de selectie suplimentare, respective un DCD cu 2k linii de iesire.

n-1, Xn-2,.X , care selecteaza la iesirea Y valoarea de pe una din cele M=2 la puterea N intrari , in-1, in-2.i prin specificatia indicelui marimii ij.

In fig. 5 se prezinta un MUX cu 2 biti de selectie X , X

Functionarea circuitului din fig.5 este descrisa de tabelul:

5: MUX cu 2 biti de selectie X , X

Multiplexorul cu 2 intrari de selectie conform fig.5. Semnalele de intrare vor avea urmatoarele forme de unda (fig.6)

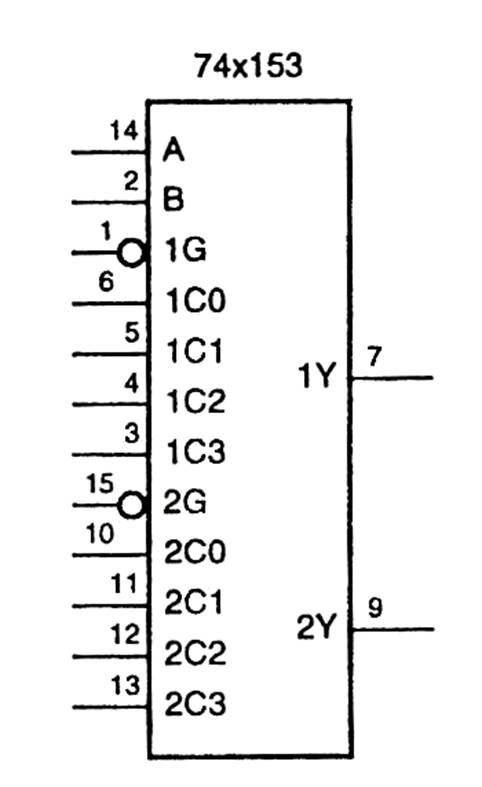

Arareori se intampla ca un multiplexor sa aiba chiar toate caracteristicile necesare pentru rezolvarea unei problem concrete. In figura 7(a) si (b), avem ca exemplu,utilizarea in schema unui procesorde calculator a unui multiplexorde 16 biti, cu 8 intrari,de tipul 74x151 sau de 16 celule ASICechivalente acestora, fiecare prelucrend cate un bit de la toate intrarile si de la iesire. Campul de 3 biti, din procesor, pentru selectarea registrelor ar trebui conectat la intrarile A,B si C ale tuturor celor 16 multiplexoare pentru ca acestea sa selecteze in orice moment acelasi registru sursa.

Dispozitivul care ar produce campul de 3 biti pentru selectarea registrelor, (din fig.7) ar trebui sa aiba capacitatea (fanout) de a comanda 16 circuite de sarcina .in cazul seriei de CI 74LS, acest lucru este posibil deoarece dispozitivele respective au, in mod normal, un fanout de 20 de circuite de sarcina TTLde tipul LS.

Avem insa si norocul ca '151 sa fi fost conceput astfel incat fiecare dintre intrarile A,B si C sa constituie cate un singur circuit de sarcina TTL LS pentru circuitele care le comanda. Teoretic, '151 ar fi putut fi realizat si fara cele trei inversoare de la primul nivel, care apar la intrarile de selectare in fig.7, dar atunci fiecare intrare de selectare ar fi fost echivalenta cu 5 sarcini TTL LS, iar pentru circuitele de comanda din aplicatia de selectare a registrelor ar fi fost necesar un fanout de 80.

Fig.7 multiplexorul de 1 bit,cu 8 intrari, 74x151: (a) schema logica, inclusiv numerotarea pinilor la capsula standard "dual in linie" cu 16 pini; (b) simbolul logic traditional.

O alta caracteristica a multiplexoarelor care se preteaza la expandare este numarul surselor de date . Ca exemplu sa presupunem ca avem nevoie de un

multiplexor de 1 bit, cu 32 de intrari. In fig.8 este prezentat un posibil miod de realizare a acestuia. Sunt necesari 5 biti de selectare. Un decodor cu 2 intrari si 4 iesiri (o jumatate dintr-un 74x139) decodeaza primii 2 biti de selectare de ordin superior, activand unul din cele 4 multiplexoare cu 8 intrari 74x151. Intrucat la un moment dat este activat un singur '151,iesirile tuturor dispozitivelor '151 pot fi combinate prin OR pentru a obtine semnalul de iesire final.

Multiplexorul de 1 bit cu 32 de intrari poate fi construit si cu 74x251. Circuiteul este identic cu cel din fig.8 ,cu exceptia faptului ca poarta NAND de la iesire dispare . in schimb ,iesirile Y ale celor patru '251 sunt conectate impreuna. Decodorul '139 face ca in orice moment cel mult unul dintre dispozitivele '251 sa aiba activate iesirile cu 3 stari. Daca '139 nu este activat, atunci unul dintre dispozitivele '251 nu este activat iar iesirile XOUT si XOUT_L sunt nedefinite. Dar, daca se doreste ,toate semnalele de iseire pot fi conectate la +5V prin rezistoare pentru ca iesirea sa fie fortata in HEIGH, in acest caz.

Multiplexoare cu ABEL si PLD

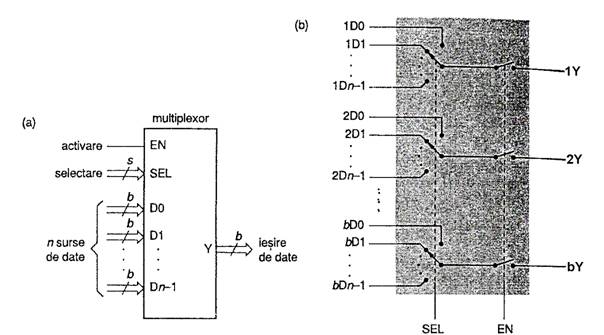

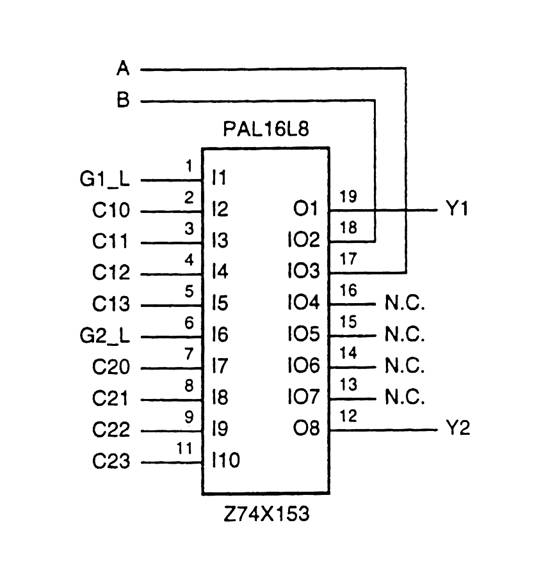

Multiplexoarele pot fi proiectate foarte usor folosind ABEL si PLD combinationale. De exemplu, functia unui multiplexor de 2 biti cu 4 intrari, de tipul 74x153 poate fi realizata cu un PAL16L8, cum arata in fig.9. Remarcam cateva caracteristici de proiectare si programe specific pentru PLD:

In programul ABEL, denumirile semnalelor sufera mici modificari fata de cele prezentate in fig.11 pt un 74x153 deoarece in ABEL nu este permisa folosirea unei cifre ca prim character in denumirea unui semnal.

74x153 are 12 intrari pe cand un PAL16L8 are doar 10. De aceea doua dintre intrarile dispozitivului '153 se repartizeaza la pinii I/O ai dispozitivului 16L8, care nu vor mai fi dispnibili ca iesiri.

Iesirile de la '153 (1Ysi 2Y) sunt repartizate la pinii 19 si 12 ai PAL16L8, care devin utilizabili numai ca iesiri. Variant aceasta este preferabila repartizarii iesirilor la pinii I/O; daca avem posibilitatea de a alege este mai bine sa avem in rezerva pinii I/O, decat pini utilizabili doar ca iesiri.

Desi ecuatiile din tabel aferente multiplexorului sunt scrise sub forma naturala a unei sume de produse, ele nu sunt aplicabile direct structurii de '16L8 din cauza inversorului dintre matricea AND-OR si pinii de iesire reali. Deci compilatorul ABEL trebuie sa complementeze ecuatiile din tabel si apoi sa aduca rezultatul la forma redusa de suma de produse. Daca se foloseste un GAL16V8 sunt aplicabile ambele variante de ecuatii.

Fig.9 Schema logica a unui PAL16L8 utilizat ca multiplexor similar cu 74x153.

Fig .10 Simbolul logic traditioanal pentru 74x153

|